SerDes戰(zhàn)爭(zhēng)升溫:博通、Marvell、聯(lián)發(fā)科爭(zhēng)奪人工智能互聯(lián)霸權(quán)

隨著AI模型以驚人速度擴(kuò)展,SerDes(串行/解串器)已成為提升芯片間數(shù)據(jù)帶寬的關(guān)鍵。據(jù)TrendForce觀察,自2025年以來(lái),高速SerDes的競(jìng)爭(zhēng)日益激烈。除了博通和Marvell,聯(lián)發(fā)科據(jù)報(bào)道通過(guò)224G SerDes進(jìn)入了谷歌的TPU生態(tài)系統(tǒng),而NVIDIA則開(kāi)始向集成電路和IP設(shè)計(jì)合作伙伴開(kāi)放其NVLink Fusion SerDes的IP。

在此背景下,SerDes能力正成為ASIC廠商的關(guān)鍵差異化因素,企業(yè)競(jìng)相加強(qiáng)互聯(lián)技術(shù)以支持AI基礎(chǔ)設(shè)施。這引發(fā)了關(guān)于SerDes是什么、為何變得如此關(guān)鍵以及哪些參與者在塑造這一快速演變格局的關(guān)鍵問(wèn)題。

SerDes是什么?

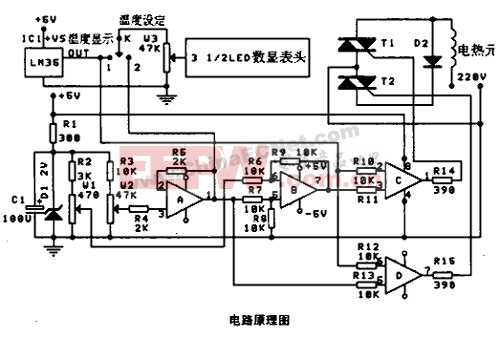

36Kr解釋說(shuō),SerDes(串行器/解串器)是一項(xiàng)基礎(chǔ)技術(shù),能夠?qū)崿F(xiàn)芯片間高速數(shù)據(jù)傳輸,旨在最大化芯片間鏈路的帶寬,同時(shí)最小化物理I/O連接數(shù)量。

TrendForce指出,SerDes通過(guò)將大量并行數(shù)據(jù)轉(zhuǎn)換為高速串行流進(jìn)行傳輸(串行化器),然后在接收端恢復(fù)為并行數(shù)據(jù)(解串器)來(lái)實(shí)現(xiàn)這一目標(biāo)。通過(guò)這樣做,該技術(shù)顯著提升了數(shù)據(jù)吞吐量,同時(shí)不增加I/O引腳。正如36Kr指出的,SerDes曾是芯片上的另一個(gè)接口模塊,在AI時(shí)代已被提升為關(guān)鍵基礎(chǔ)設(shè)施——這是決定系統(tǒng)擴(kuò)展能力的關(guān)鍵因素。

ASIC廠商在SerDes競(jìng)技場(chǎng)上競(jìng)爭(zhēng)

TrendForce觀察到,高速SerDes市場(chǎng)的競(jìng)爭(zhēng)主要集中在兩個(gè)主要陣營(yíng):既有的SerDes知識(shí)產(chǎn)權(quán)廠商如Synopsys和Cadence,以及ASIC設(shè)計(jì)公司在內(nèi)部開(kāi)發(fā)SerDes能力。

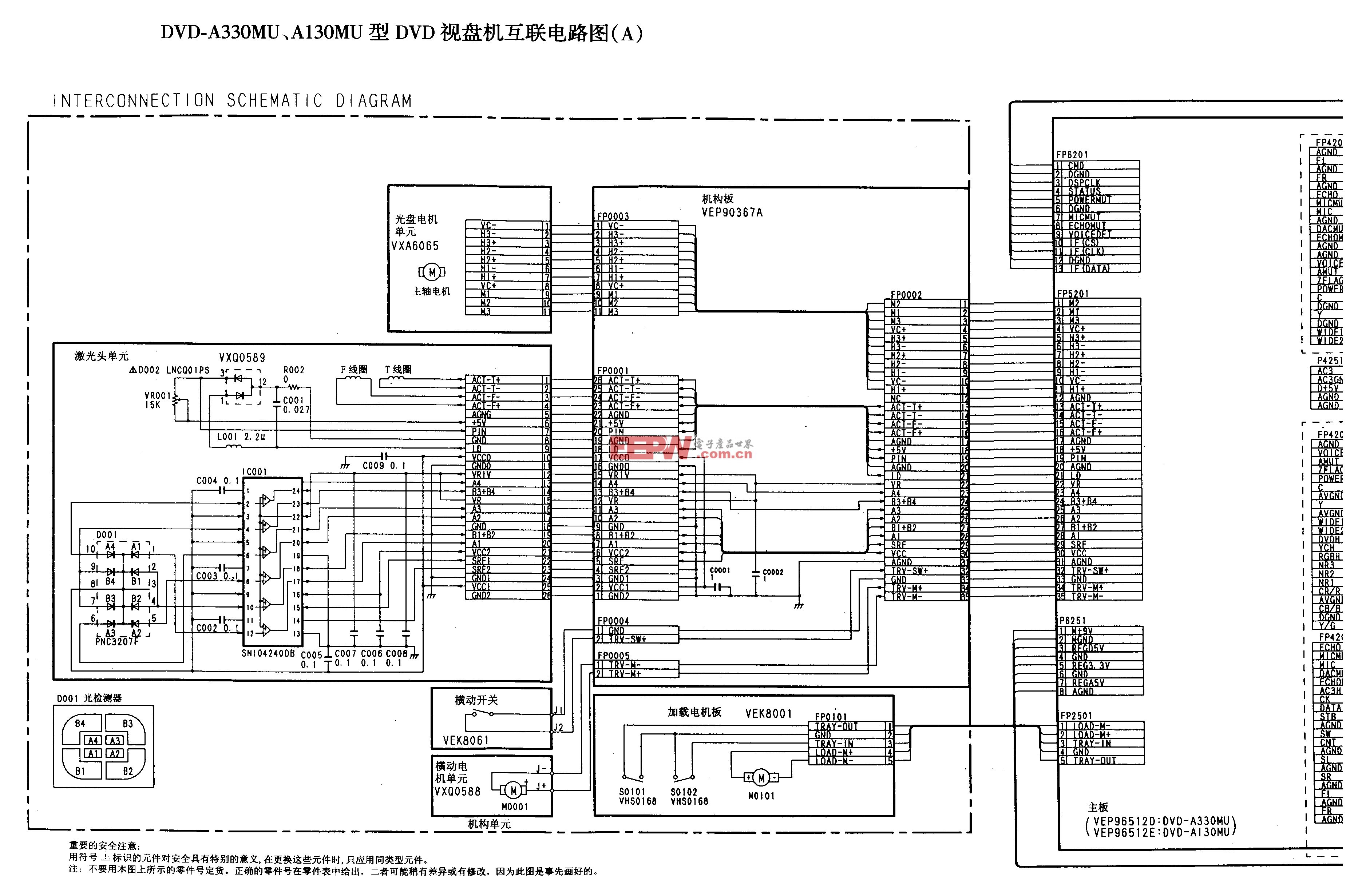

36Kr指出,領(lǐng)先的ASIC設(shè)計(jì)公司如博通和Marvell也是SerDes的強(qiáng)大力量,這絕非巧合,因?yàn)樵摷夹g(shù)確保了芯片間連接的可靠性。其中,博通的數(shù)據(jù)中心Tomahawk交換機(jī)本質(zhì)上是SerDes密度怪獸:Tomahawk 5(51.2T)集成了多達(dá)64個(gè)Peregrine SerDes核心,每個(gè)核心配備8個(gè)106Gbps的PAM4收發(fā)器和PCS,報(bào)告補(bǔ)充道。

Tomahawk 6 于六月開(kāi)始發(fā)貨,采用芯片組架構(gòu),支持 100G/200G SerDes 以及聯(lián)合封裝光學(xué)元件(CPO)。據(jù)路透社報(bào)道,該產(chǎn)品專為超過(guò)一百萬(wàn)XPU的AI集群設(shè)計(jì),提供全面的AI路由和互聯(lián)功能,采用臺(tái)積電3nm工藝制造。

另一方面,36Kr指出,博通的SerDes以高性能和深度集成著稱,Marvell的優(yōu)勢(shì)在于協(xié)議廣度和先進(jìn)的流程節(jié)點(diǎn)適應(yīng)性。值得注意的是,報(bào)告指出Marvell在PCIe SerDes節(jié)奏方面領(lǐng)先Broadcom,使其在服務(wù)器端HBM連接和存儲(chǔ)控制器市場(chǎng)占據(jù)決定性優(yōu)勢(shì)。

Marvell也在先進(jìn)節(jié)點(diǎn)競(jìng)賽中不斷前進(jìn),2025年推出了其首款用于次世代AI和云基礎(chǔ)設(shè)施的2納米硅IP,采用臺(tái)積電2nm工藝生產(chǎn)。正如公司所說(shuō),該平臺(tái)聚焦于廣泛的半導(dǎo)體知識(shí)產(chǎn)權(quán)組合,包括電氣和光學(xué)SerDes、2D/3D單片互連、先進(jìn)封裝、硅光子學(xué)、定制HBM計(jì)算架構(gòu)、片上SRAM、SoC結(jié)構(gòu)以及如PCIe Gen 7等高速接口。

聯(lián)發(fā)科崛起為SerDes競(jìng)爭(zhēng)者

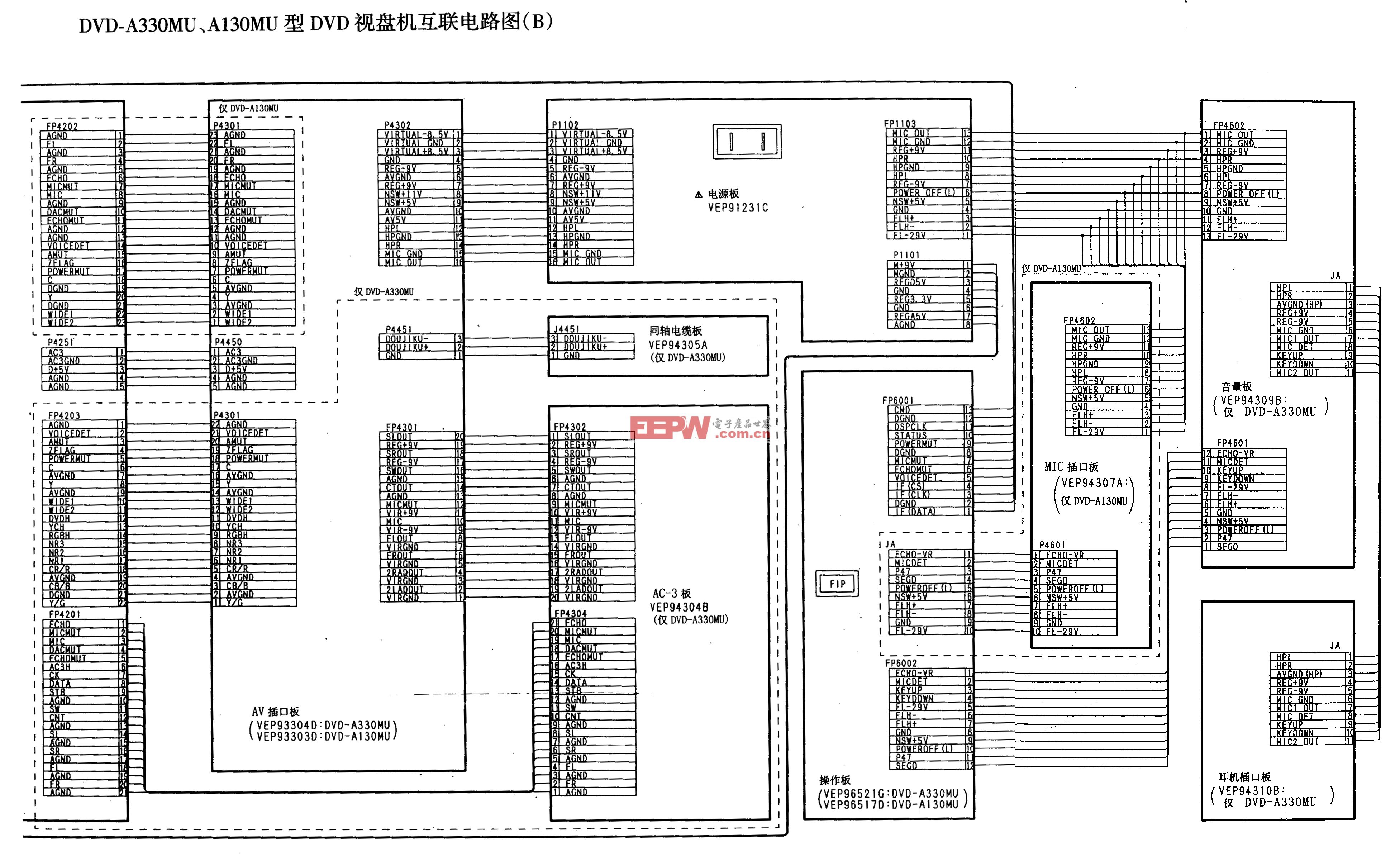

值得注意的是,TrendForce指出,聯(lián)發(fā)科已成為強(qiáng)勁競(jìng)爭(zhēng)者,其SerDes已提升至200G,400G知識(shí)產(chǎn)權(quán)項(xiàng)目計(jì)劃于2026年推出。據(jù)TrendForce報(bào)道,AI芯片將在2026年底轉(zhuǎn)向224G SerDes,而聯(lián)發(fā)科的224G能力正成為贏得TPU v8e(斑馬魚(yú))項(xiàng)目及更遠(yuǎn)項(xiàng)目的關(guān)鍵。

據(jù)《商業(yè)時(shí)報(bào)》報(bào)道,聯(lián)發(fā)科在云ASIC市場(chǎng)的立足點(diǎn)建立在其長(zhǎng)期的SerDes專業(yè)領(lǐng)域:目前,聯(lián)發(fā)科的112Gb/s SerDes數(shù)字信號(hào)處理器采用PAM-4接收機(jī)架構(gòu),在4納米工藝上實(shí)現(xiàn)超過(guò)52dB的損耗補(bǔ)償,保持低信號(hào)衰減和高干擾抗阻——這對(duì)數(shù)據(jù)中心和先進(jìn)封裝至關(guān)重要。報(bào)告指出,其專為數(shù)據(jù)中心應(yīng)用設(shè)計(jì)的224G SerDes已完成硅片驗(yàn)證,并因其技術(shù)成熟度吸引了業(yè)界高度關(guān)注。

然而,TrendForce 指出,SerDes 市場(chǎng)競(jìng)爭(zhēng)日益激烈,224G SerDes 開(kāi)發(fā)和光學(xué)引擎集成成為關(guān)鍵差異化因素,當(dāng)前 ASIC 廠商面臨挑戰(zhàn)。TrendForce 援引聯(lián)發(fā)科管理層的言論指出,隨著數(shù)據(jù)速率持續(xù)攀升,傳統(tǒng)銅線互連正觸及物理極限。因此,超越400G技術(shù),技術(shù)必然會(huì)進(jìn)入光學(xué)領(lǐng)域,這也是行業(yè)未來(lái)投資的關(guān)鍵重點(diǎn)。

評(píng)論