HBM4與SPHBM4:為人工智能和高性能計算拓展內存帶寬

JEDEC制定的第四代高帶寬內存(HBM4)標準,以及新興的第四代片上封裝高帶寬內存(SPHBM4)標準,實現了帶寬提升與封裝方案的拓展,助力人工智能和高性能計算系統突破內存與輸入輸出壁壘。

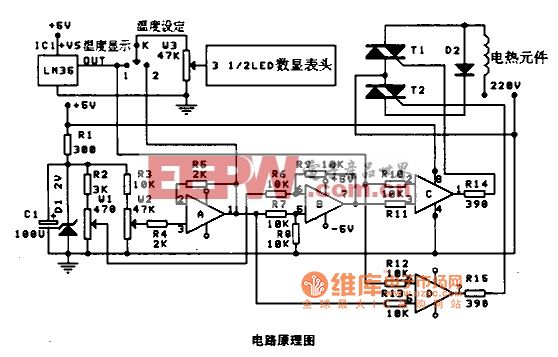

過去二十年,高性能計算(HPC)和人工智能(AI)系統所使用處理器的原始計算能力實現了跨越式增長。圖 1 展示了這一發展趨勢:同一時期內,異構處理器(XPU)的浮點運算性能提升了逾 9 萬倍,而動態隨機存取存儲器(DRAM)的帶寬和互連帶寬僅提升了約 30 倍。

圖1 20 年間 XPU 性能與互連帶寬的增長情況。

這種計算能力與數據傳輸能力之間不斷擴大的差距 —— 即業界常說的內存壁壘與輸入輸出(I/O)壁壘,已成為制約系統實際性能發揮的最關鍵因素之一。

對于系統設計人員而言,這種失衡直接導致計算資源利用率不足、功耗攀升,以及系統架構復雜度不斷增加。因此,在推動人工智能性能升級的過程中,內存帶寬和封裝技術的重要性,已與晶體管密度、核心數不相上下。

高帶寬內存(HBM):現代人工智能架構的基石

為應對上述帶寬挑戰,高性能計算和人工智能系統正越來越多地采用以芯粒為核心的解耦架構。盡管低功耗雙倍數據率內存(LPDDR)和雙倍數據率內存(DDR)仍發揮著重要作用,但高帶寬內存(HBM)已成為目前可用的帶寬最高的 DRAM 解決方案,也是賦能現代加速器的核心技術。

HBM 器件由底部的緩沖芯粒(或基底芯粒)和上方多層三維堆疊的 DRAM 芯粒構成。緩沖芯粒采用超細間距微凸點技術,借助硅中介層、硅橋等先進封裝技術,可將內存堆疊與專用集成電路(ASIC)合封在一起。

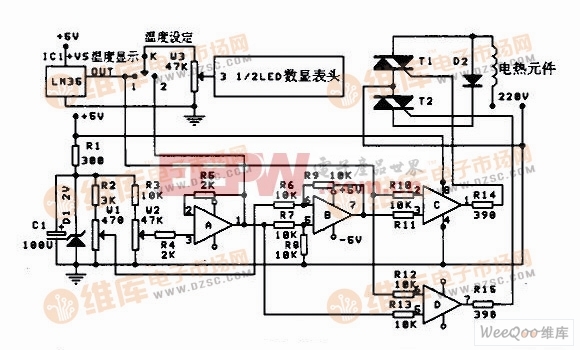

在杰德克(JEDEC)HBM 任務組制定的嚴格標準支撐下,HBM 已成為量產系統中,基于芯粒集成技術的最成功、應用最廣泛的范例之一。圖 2 為 HBM DRAM 堆疊通過硅中介層與 ASIC 相連的典型側視圖。

圖 2 HBM DRAM 堆疊通過硅中介層與 ASIC 相連的典型側視圖。

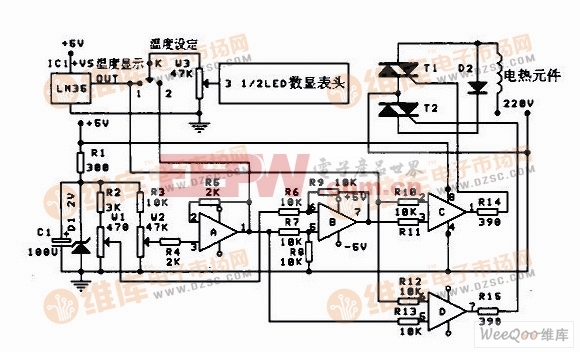

HBM 的一個典型商用案例是英偉達的 B100 “布萊克韋爾” 加速器(圖 3)。該封裝內包含兩顆掩模版尺寸的大型 XPU 芯粒,二者通過高帶寬鏈路互連,HBM 器件則排布在每顆芯粒的上下邊緣。每顆 XPU 芯粒集成四組 HBM 堆疊(每條長邊兩組),使得單個封裝內的 HBM 器件總數達到八組。

以 JEDEC 敲定 HBM3 標準時的典型規格為例,每組 HBM3 器件可采用 8 層堆疊的 16Gb DRAM 芯粒,單堆疊容量為 16GB。憑借 6.4Gb/s 的數據傳輸速率和 1024 個輸入輸出接口,每組 HBM3 器件的帶寬可達約 0.8TB/s。八組器件協同工作時,該配置能提供 128GB 的總內存容量,以及約 6.6TB/s 的聚合帶寬。

圖 3 英偉達的 B100 “布萊克韋爾” 加速器

第四代高帶寬內存(HBM4):帶寬與容量的雙重升級

為實現內存性能與計算能力的同步提升,JEDEC 近期正式發布了 JESD270-4,即 HBM4 標準。相較于 HBM3,HBM4 在架構上進行了多項改進,可直接滿足人工智能工作負載日益增長的帶寬和容量需求。

HBM4 最核心的改進之一是將通道數翻倍,輸入輸出接口從 1024 個增加至 2048 個。同時,其支持的數據傳輸速率提升至 6~8Gb/s 及以上;內存密度也實現升級,不僅納入了 24Gb 和 32Gb 規格的 DRAM 芯粒,還支持 12 層和 16 層的堆疊方式;包括動態刷新管理(DRFM)在內的可靠性、可用性和可維護性(RAS)特性也得到了增強。

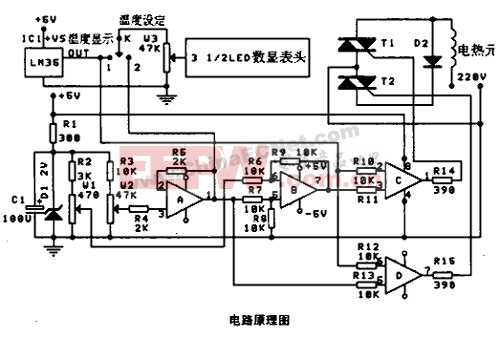

綜合這些改進,HBM4 在帶寬、能效和容量上均較 HBM3 實現了質的提升。例如,采用 16 層堆疊 32Gb 芯粒的 HBM4e 器件,單器件容量可達 64GB(圖 4)。

憑借 2048 個工作在 8Gb/s 的輸入輸出接口,這類器件的單通道帶寬最高可達 2TB/s。單個封裝內若集成八組 HBM4 器件,總內存容量可提升至 512GB(是前述 HBM3 案例的 4 倍),聚合帶寬則突破 16TB/s,實現 2.5 倍的提升。

定制化 HBM 與基底芯粒的核心作用

隨著 HBM4 的加速普及,部分系統設計人員開始研發針對特定應用優化的定制化 HBM 解決方案,而這一趨勢的關鍵支撐,正是 HBM 基底芯粒的技術演進。

在早期的 HBM 產品中,基底芯粒通常采用 DRAM 優化工藝制造,該工藝雖適用于電容結構制作,卻并非高速邏輯電路的最優選擇。而在 HBM4 時代,多數供應商正將基底芯粒的制造工藝切換為標準先進邏輯工藝。這一轉變不僅與片上系統(SoC)設計人員所熟悉的工藝更契合,也為定制化開發打開了大門。

無論使用標準還是定制化 HBM4 器件,其解決方案仍需依托先進封裝技術和硅基襯底(如中介層、硅橋),以實現內存與 ASIC 之間大量超細間距的互連。

第四代標準封裝高帶寬內存(SPHBM4):讓有機封裝也能實現 HBM 級帶寬

盡管傳統 HBM 在性能上優勢顯著,但其集成過程需要先進封裝技術支撐,這會推高成本和設計復雜度。許多系統設計人員,尤其是聚焦量產和可靠性的設計人員,更傾向于使用標準有機襯底。為填補這一技術空白,JEDEC 宣布,標準封裝高帶寬內存(SPHBM4)新標準的制定已接近完成。

SPHBM4 器件采用與 HBM4 完全相同的 DRAM 核心芯粒,能提供同等的聚合帶寬,同時全新設計了一款接口基底芯粒,專門適配標準有機襯底的貼裝需求。圖 5 為 SPHBM4 DRAM 與 ASIC 一同直接貼裝在有機封裝襯底上的側視圖。其中 ASIC 既可同樣貼裝在有機襯底上,也可保留在硅橋等先進封裝結構上,以實現多 XPU 集成。

為通過更少的引腳實現 HBM4 級別的吞吐率,SPHBM4 采用了更高的接口工作頻率和串行化技術。HBM4 定義了 2048 路數據信號,而 SPHBM4 預計將采用 512 路數據信號并搭配 4:1 串行化方案,從而實現有機襯底所需的寬松凸點間距。

由于 SPHBM4 與 HBM4 使用相同的 DRAM 堆疊,單堆疊容量保持不變。但有機襯底的布線工藝支持 SoC 與內存之間更長的通道長度,這為系統級設計的權衡取舍創造了新可能。尤其是更長的布線距離和斜向走線設計,通常能讓單顆芯粒周圍排布更多的內存堆疊。

圖 6 展示了這一設計優勢:當 HBM 器件貼裝在硅基襯底上時,必須緊鄰 XPU 擺放,這使得每 25 毫米的芯粒邊緣最多只能排布兩組內存堆疊;而將 SPHBM4 貼裝在有機襯底上時,同一段邊緣可連接三組內存器件,內存容量和帶寬均可實現約 50% 的提升。

即便 XPU 下方仍需使用硅基襯底(例如為了實現高帶寬的 XPU 間互連),將內存器件轉移至有機封裝后,中介層的整體尺寸也能大幅縮小,這將為系統在成本、可制造性和測試復雜度上帶來實質性改善。

未來展望

人工智能工作負載仍在不斷突破內存帶寬、容量和封裝技術的極限,JEDEC 發布的 HBM4 標準是應對這些需求的重要一步,而新興的 SPHBM4 標準則通過讓標準有機襯底實現 HBM 級性能,進一步拓展了設計空間。

對于系統架構師而言,這些技術為平衡性能、成本和集成復雜度提供了全新的靈活性。隨著內存和封裝技術對整體系統能力的影響愈發顯著,盡早考量 HBM4、定制化 HBM 和 SPHBM4 等技術方案,將成為充分釋放下一代人工智能和高性能計算性能的關鍵。

評論