新思科技:硬件再度成為行業(yè)核心

硬件輔助驗證技術(shù)四十年演進 —— 從在線仿真到人工智能時代的全棧驗證

十多年來,硬件輔助驗證平臺一直是驗證工具集的核心。如今,任何重要的半導(dǎo)體項目流片,都離不開仿真或現(xiàn)場可編程門陣列(FPGA)原型驗證的核心支撐。該技術(shù)已深度融入芯片研發(fā)流程,以至于人們?nèi)菀渍`以為它自始至終都是行業(yè)標配。

但事實并非如此。

若對確切起源稍作放寬,今年大致是硬件輔助驗證技術(shù)誕生 40 周年,這一概念廣義上涵蓋硬件仿真和 FPGA 原型驗證兩大技術(shù)。四十年來,硬件輔助驗證從一種小眾技術(shù),發(fā)展成為現(xiàn)代芯片研發(fā)不可或缺的核心支柱。從諸多方面來看,它的發(fā)展歷程也是半導(dǎo)體行業(yè)的縮影:隨著芯片復(fù)雜度不斷提升、軟件逐步占據(jù)主導(dǎo)地位、人工智能開始重塑一切,硬件輔助驗證的應(yīng)用價值也在不斷被重新定義。

在硬件輔助驗證成為公認的技術(shù)門類之前,已有相關(guān)技術(shù)雛形。例如,IBM 曾通過約克鎮(zhèn)仿真引擎、后續(xù)的工程驗證引擎等系統(tǒng),開展硬件加速技術(shù)的實驗。這類設(shè)備本質(zhì)上是仿真加速器 —— 為比傳統(tǒng)軟件仿真器更快運行硬件模型而設(shè)計的專用計算機。它們代表著技術(shù)的重要進步,但本質(zhì)上仍依附于仿真范式:雖提升了運行速度,卻遠不足以將真實場景應(yīng)用于被測設(shè)計。

硬件輔助驗證平臺則屬于另一類技術(shù)架構(gòu)。早期仿真器依托可重編程硬件(通常為 FPGA 陣列)進行配置,以模擬被測設(shè)計的行為。工程師首次能夠在芯片流片前,以接近實際的運行速度與芯片的仿真模型進行交互。PiE 設(shè)計系統(tǒng)、Quickturn、IKOS、Zycad 等公司成為這一全新驗證技術(shù)的先驅(qū),為其發(fā)展成為半導(dǎo)體研發(fā)的核心支柱奠定了基礎(chǔ)。

硬件輔助驗證的發(fā)展歷程可大致劃分為三個時代:硬件復(fù)雜度的提升催生仿真技術(shù)的早期時代;軟件占據(jù)主導(dǎo)、硬件輔助驗證向虛擬環(huán)境延伸的中期時代;以及人工智能工作負載推動硬件重回架構(gòu)創(chuàng)新核心的成熟時代。

早期時代:硬件復(fù)雜度攀升推動仿真技術(shù)崛起

上世紀 80 年代初,半導(dǎo)體設(shè)計幾乎完全由硬件定義,即便存在嵌入式軟件,也僅發(fā)揮次要作用。彼時的行業(yè)由處理器和圖形芯片領(lǐng)域的先驅(qū)推動,向著當時堪稱驚人的里程碑 —— 百萬門級芯片邁進。驗證工作主要依賴門級仿真,這也是當時的通用行業(yè)標準。

然而,隨著設(shè)計規(guī)模不斷擴大,仿真器遭遇了難以突破的性能瓶頸:主機內(nèi)存有限,不得不將設(shè)計數(shù)據(jù)換入磁盤;仿真運行時間大幅增加,測試向量數(shù)量呈爆炸式增長;要實現(xiàn)合格的故障覆蓋率,所需的計算量已達到難以管控的程度。流片前的全系統(tǒng)驗證即便并非完全不可能,也已變得愈發(fā)不切實際。行業(yè)亟需一種速度更快、更貼近實際芯片的驗證技術(shù)。

硬件輔助驗證技術(shù)應(yīng)運而生,成為應(yīng)對這一行業(yè)危機的解決方案。早期的硬件輔助驗證平臺主要以在線仿真模式部署:將仿真器通過物理線纜接入實際的目標系統(tǒng),工程師得以在搭載真實外設(shè)的實際環(huán)境中對被測設(shè)計進行測試。這一突破具有革命性意義:設(shè)計人員不再依賴人工生成的測試向量,而是能夠通過真實工作負載驗證芯片,實現(xiàn)了人工仿真向量無法企及的真實度,驗證工作首次能夠模擬芯片實際應(yīng)用中的表現(xiàn)。

這項技術(shù)的發(fā)展前景廣闊,但早期的實際應(yīng)用卻困難重重。初代仿真器的搭建流程復(fù)雜、操作要求嚴苛、且易出現(xiàn)故障:漫長的搭建周期常常導(dǎo)致驗證工作無法按期完成;由線纜和硬件依賴引發(fā)的可靠性問題,造成設(shè)備頻繁停機;平均無故障工作時間以小時計,而非數(shù)周或數(shù)月,驗證團隊不得不將更多精力用于調(diào)試仿真器本身,而非被測設(shè)計。盡管如此,行業(yè)發(fā)展的趨勢已然明確:驗證工作已無法再單純依靠軟件完成。

中期時代:軟件席卷行業(yè),硬件輔助驗證成驗證核心支柱

在隨后的數(shù)十年里,產(chǎn)品功能開始從硬件逐步向軟件代碼遷移,芯片設(shè)計格局發(fā)生了深刻變革。馬克?安德森在 2011 年提出的 “軟件正在吞噬整個世界” 這一觀點,精準捕捉到了這一趨勢。他的預(yù)言在幾乎所有與計算機相關(guān)的行業(yè)中,都得到了驚人的印證。片上系統(tǒng)(SoC)成為軟件定義的平臺,其智能特性更多體現(xiàn)在固件、操作系統(tǒng)、驅(qū)動程序和應(yīng)用棧中。硬件不再是產(chǎn)品的全部,而是承載軟件代碼的基礎(chǔ)載體。

這一轉(zhuǎn)型徹底改變了驗證工作的模式:靜態(tài)測試模式已無法應(yīng)對現(xiàn)代設(shè)計的全部復(fù)雜度。工程師轉(zhuǎn)而采用軟件驅(qū)動的激勵方式,通過高級測試平臺對各類功能領(lǐng)域的芯片行為進行驗證;硬件驗證語言和更抽象的驗證方法學(xué)也隨之出現(xiàn),以適配這一新的行業(yè)現(xiàn)實。

曾主要用于實時在線仿真驗證的硬件輔助驗證引擎,也完成了適配升級,成為這些以軟件為核心的驗證環(huán)境的底層執(zhí)行引擎。行業(yè)通過基于事務(wù)的驗證技術(shù)(由電氣和電子工程師協(xié)會 SCE-MI 標準規(guī)范化),實現(xiàn)了軟件測試平臺與硬件映射被測設(shè)計之間的標準化交互。工程師不再需要逐周期切換信號,而是能夠通過高級事務(wù)與被測設(shè)計進行交互,驗證性能和研發(fā)效率得到了大幅提升。

這一轉(zhuǎn)變也突破了早期技術(shù)的諸多實際限制:虛擬化環(huán)境減少了對物理連接的依賴,摒棄了在線仿真架構(gòu)中所需的速度適配器;驗證知識產(chǎn)權(quán)(IP)取代了硬件接口,打造出可擴展的純數(shù)字化驗證生態(tài)。

隨著行業(yè)逐步推行左移設(shè)計理念,硬件輔助驗證平臺成為實現(xiàn)這一理念的最強力支撐。它讓工程師能夠在設(shè)計流程的極早期階段進行軟件開發(fā),從裸機初始化開始,逐步延伸至驅(qū)動程序和操作系統(tǒng)的開發(fā)。驗證工作不再局限于孤立的功能正確性檢測,而是在芯片物理實體誕生前,就已覆蓋整個軟硬件系統(tǒng)的行為驗證。

至此,硬件輔助驗證已遠不止是提升驗證速度的工具,更逐漸成為連接硬件與軟件開發(fā)的橋梁,推動研發(fā)團隊從串行工作轉(zhuǎn)向并行協(xié)作,也確立了其作為現(xiàn)代系統(tǒng)驗證核心支柱的行業(yè)地位。

人工智能時代:硬件重獲核心地位,硬件輔助驗證邁入全棧時代

2010 年代中期起,在人工智能爆發(fā)式發(fā)展的推動下,半導(dǎo)體行業(yè)邁入全新時代。行業(yè)發(fā)展的敘事也從 “軟件吞噬世界”,演變?yōu)楦鼜氐椎?“軟件定義硬件”。在人工智能時代,軟件不再只是運行在硬件之上,而是愈發(fā)深刻地定義著硬件的設(shè)計方向。現(xiàn)代人工智能模型的極致需求,正從底層重塑處理器的架構(gòu)設(shè)計。

生成式人工智能暴露了傳統(tǒng)通用架構(gòu)的局限性:其海量的數(shù)據(jù)交互需求和超高的計算強度,讓中央處理器(CPU)難以承受,即便是高度優(yōu)化的系統(tǒng)也面臨巨大壓力。為跟上技術(shù)發(fā)展步伐,行業(yè)開始采用專用架構(gòu),包括圖形處理器(GPU)、現(xiàn)場可編程門陣列(FPGA),以及圍繞大規(guī)模并行計算和張量計算設(shè)計的專用人工智能加速器。

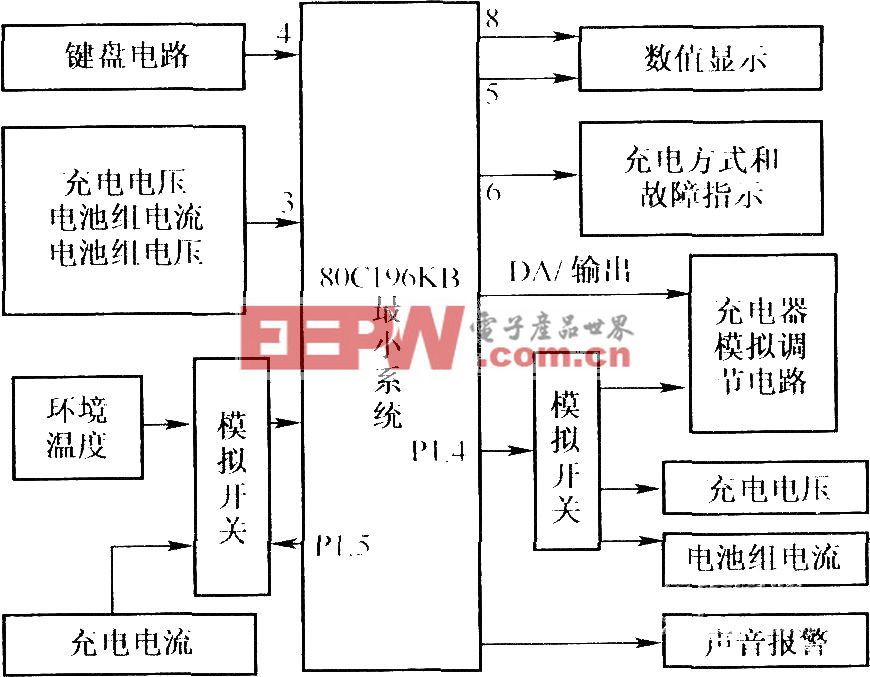

這些技術(shù)發(fā)展大幅提升了片上系統(tǒng)設(shè)計的規(guī)模和復(fù)雜度:人工智能時代的芯片通常包含數(shù)十億門級電路、異構(gòu)計算集群,以及能實現(xiàn)處理單元間高效數(shù)據(jù)交互的先進片上網(wǎng)絡(luò)(NOC)。詳見圖 1。

圖 1:人工智能處理器高層級框圖

(注:框圖包含以下核心模塊:針對神經(jīng)網(wǎng)絡(luò)工作負載優(yōu)化的人工智能處理器、高帶寬內(nèi)存堆疊、PCIe/NVLink 接口、片上靜態(tài)隨機存取存儲器、矩陣 / 張量計算核心、片上網(wǎng)絡(luò)網(wǎng)格)

在這一行業(yè)背景下,硬件輔助驗證的應(yīng)用價值得到了根本性的拓展。

驗證工作不再局限于十億門級以下設(shè)計的功能正確性檢測,而是需要適配數(shù)十億門級的系統(tǒng),驗證范圍也遠不止邏輯層面和軟件棧:如今的硬件輔助驗證平臺正被廣泛用于評估芯片的功耗與熱性能、分析運行表現(xiàn)、驗證安全需求、捕捉全系統(tǒng)級的交互行為,以及運行能模擬設(shè)計實際應(yīng)用場景的真實工作負載。

與此同時,在線仿真模式也已發(fā)展成為一項關(guān)鍵的工程能力,而非過時的技術(shù)模式。這一點在全速 FPGA 原型驗證中尤為明顯:在設(shè)計投入量產(chǎn)前,必須通過該技術(shù)對真實的物理接口進行全速驗證。通過讓被測設(shè)計在研發(fā)早期就能與實際的物理層(PHY)硬件交互,在線仿真技術(shù)能發(fā)現(xiàn)純虛擬環(huán)境中無法暴露的集成、時序和信號完整性問題,從而在流片前大幅提升硬件和軟件設(shè)計的可靠性。

同樣重要的是,人工智能硬件與其軟件生態(tài)密不可分。編譯器、運行時環(huán)境、函數(shù)庫、計算核心和部署框架不再是后續(xù)補充的環(huán)節(jié),而是決定硬件成敗的關(guān)鍵。因此,硬件輔助驗證平臺被用于在芯片物理實體誕生前,運行真實的人工智能工作負載,確保軟硬件協(xié)同演進,而非串行開發(fā)。架構(gòu)設(shè)計與實際運行之間的反饋循環(huán),也愈發(fā)多地在流片前完成,而非等到首片芯片投片之后。

從這個意義上來說,人工智能時代的驗證工作已真正邁入全棧時代。硬件輔助驗證不再只是一項驗證工具,更成為軟硬件協(xié)同設(shè)計的融合載體,催生了一種全新的行業(yè)范式 ——軟件驅(qū)動的流片。

結(jié)語:硬件輔助驗證 —— 軟硬件融合的核心引擎

歷經(jīng)四十年演進,半導(dǎo)體行業(yè)完成了一次輪回:硬件復(fù)雜度的提升,讓仿真技術(shù)成為行業(yè)實際需求的必然產(chǎn)物;隨后的軟件時代拓展了硬件輔助驗證的應(yīng)用邊界,使其與虛擬環(huán)境、更豐富的軟件棧和更廣泛的系統(tǒng)級研發(fā)流程深度融合;如今,人工智能革命正再次重塑行業(yè)格局,讓硬件重回創(chuàng)新核心,也對技術(shù)的專用化、效率和規(guī)模提出了前所未有的要求。

然而,最根本的變化在于 “核心地位” 的內(nèi)涵:硬件不再是先設(shè)計、后編程的獨立環(huán)節(jié)。本十年的核心行業(yè)趨勢是軟件定義設(shè)計—— 芯片架構(gòu)的塑造,既取決于晶體管、互連線路和邏輯結(jié)構(gòu),也同樣受制于編譯器、運行時環(huán)境和工作負載需求。軟硬件之間的界限已逐漸模糊,融合成為一個緊密耦合的工程問題。

硬件輔助驗證平臺正處于這一融合的核心節(jié)點,其定位已不再是孤立的正確性檢測工具,而是驗證架構(gòu)設(shè)計意圖的關(guān)鍵環(huán)境:在這里,硬件與真實軟件實現(xiàn)交互,性能假設(shè)在真實工作負載下得到驗證,系統(tǒng)級的設(shè)計權(quán)衡在仍可進行有效設(shè)計修改的階段被充分暴露。在軟件驅(qū)動流片的時代,硬件輔助驗證成為了芯片物理實體誕生前,實現(xiàn)設(shè)計閉環(huán)的核心機制。

硬件再度成為行業(yè)核心,并非因為軟件的重要性下降,而是因為軟件的重要性已達到全新高度,甚至開始定義硬件本身。

行業(yè)的成功評判標準也隨之發(fā)生轉(zhuǎn)變:選擇硬件輔助驗證平臺,不再只是看其能驗證多少門級電路的功能正確性,而是看其能否在流片前,對軟件驅(qū)動的各類應(yīng)用場景進行完整的運行、分析和優(yōu)化。在這個新時代,硬件不再只是軟件創(chuàng)新的基礎(chǔ),更已成為推動軟件創(chuàng)新的核心引擎之一。

評論