如何選擇精密放大器拓撲

在精密信號鏈中,傳感器之后的第一個模塊通常是放大器電路,放大器電路必須放大目標信號,同時保證信號不失真。本文將討論如何為傳感器應(yīng)用選擇適當?shù)?a class="contentlabel" href="http://m.cqxgywz.com/tech/s/k/精密放大器">精密放大器電路拓撲,并重點關(guān)注運算放大器、差動放大器、電流檢測放大器、儀表放大器和全差動放大器。

引言

精密傳感器長期以來一直是測量物理世界諸多參數(shù)的關(guān)鍵元件。隨著精密測量應(yīng)用的種類和數(shù)量增加,工程師設(shè)計的系統(tǒng)需要能夠在干擾信號存在的情況下檢測到較小幅度信號,同時保證信號不失真。這不僅需要選擇適當?shù)膫鞲衅鳎€需要精心設(shè)計完整的信號路徑(從傳感器到數(shù)據(jù)轉(zhuǎn)換器),從而將模擬信號數(shù)字化。那么,對于特定的傳感器應(yīng)用而言,哪種放大器拓撲最為合適呢?選擇時,需要考慮最終系統(tǒng)的目標和放大器電路的設(shè)計優(yōu)先級。

在選擇放大器拓撲時,首先要考慮的通常是確定傳感器輸出(和放大器輸入)信號是單端信號還是差分信號。一些拓撲配置接受單端輸入信號,一些則接受差分信號。此外,選擇哪種放大器拓撲最合適將取決于我們希望放大器輸出單端信號還是差分信號。

單端運算放大器拓撲

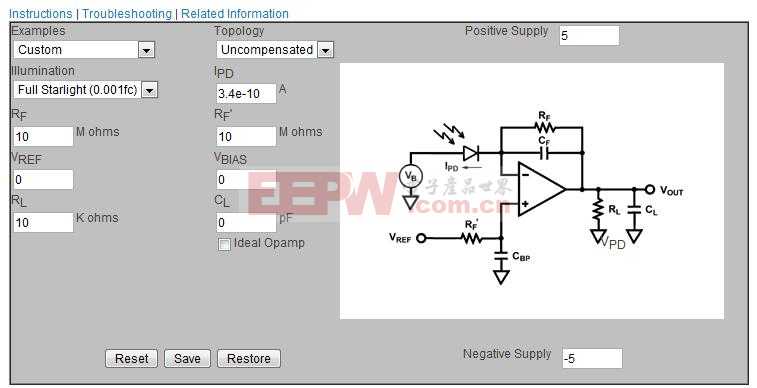

運算放大器(op amp)是一種用途極其廣泛的放大器,最開始的設(shè)計目的是完成計算器所需的各種運算功能,因此而得名。如果是具有單端輸入和單端輸出的放大器電路,將使用由一對電阻提供適當反饋的簡單運算放大器電路。當使用單端運算放大器電路來放大高精度信號時,通常在同相放大器和反相放大器這兩種拓撲之間進行選擇(圖1)。這兩種電路均采用一個反饋電阻和一個增益電阻。

圖1.單端(a)同相放大器和(b)反相放大器。

圖2顯示了簡單的單端輸入、單端輸出應(yīng)用。ADI TMP35溫度傳感器輸出的電壓與溫度成比例,靈敏度為10 mV/°C。然后,輸出信號連接到單端同相放大器電路,傳遞函數(shù)為VOUT = G × VIN,其中G是電路的閉環(huán)增益,等于1 + (R2/R1)。例如,要檢測0°C至50°C的溫度范圍,傳感器的滿量程輸出范圍將為10 mV/°C × 50°C = 500 mV。如果傳感器輸出要驅(qū)動具有5 V滿量程輸入范圍的模數(shù)轉(zhuǎn)換器(ADC),信號將需要按10 V/V的增益放大,以便利用ADC的整個輸入動態(tài)范圍。這可通過同相運算放大器電路實現(xiàn),其中G = 1 + (9 kΩ/1 kΩ) = 10 V/V。

圖2.單端溫度傳感器輸出和同相放大器電路。

共模抑制

在放大器拓撲之間選擇時,一個需要評估的關(guān)鍵因素是放大器電路有效抑制共模輸入電壓的能力(防止兩個輸入端所共有的信號電壓在輸出端表現(xiàn)出來),同時放大差模輸入電壓。共模抑制比(CMRR)是一個定量指標,用于衡量放大器電路在這方面的能力。CMRR越高,輸出端的誤差就越小。CMRR通常表示為兩個增益之比:差模電壓增益(ADIFF)相對于共模電壓增益(ACM)的值,單位為dB。

回想一下,理想運算放大器的輸入端之間存在虛短,施加于一個輸入端(+IN)的信號電壓也將出現(xiàn)在另一個輸入端(-IN);這就是運算放大器的共模電壓。現(xiàn)代運算放大器的CMRR規(guī)格可達120 dB至140 dB,甚至更高。此級別的CMRR可使共模誤差保持在最低水平,從而在輸出端實現(xiàn)高精度。舉個例子,如果運算放大器的CMRR規(guī)格為140 dB,僅0.00001%(或0.1 ppm)的運算放大器輸入端共模電壓將出現(xiàn)在輸出端(VOUT)。對于最大輸入范圍為5 V的低壓運算放大器,輸出端的最大共模誤差將僅為0.5 μV。但是,使用具有高輸入電壓范圍(例如50 V)的運算放大器會導致輸出端出現(xiàn)5 μV的誤差。這是否成為一個問題,取決于系統(tǒng)設(shè)計的要求。如果共模誤差超出特定系統(tǒng)設(shè)計的可接受限度,則需要使用能夠最大限度減少這種誤差的電路。

在同相拓撲(圖1a)中,運算放大器輸入+IN和–IN將等于信號輸入(VIN),因此信號電壓的任何增加都會導致運算放大器輸入引腳處的共模電壓增加,并且輸出端的共模誤差也會增加。或者,考慮使用反相放大器電路(圖1b)。在此拓撲中,+IN輸入(于是–IN輸入)接地。由于輸入共模電壓為0V,因此可以避免輸入端的任何共模電壓,以及由此產(chǎn)生的輸出端共模誤差。

差動放大器

許多傳感器將其輸出呈現(xiàn)為差分信號,測量的物理特性由兩個電壓之差來表示。使用具有差分輸出的傳感器的一個好處是,具有差分輸入和高共模抑制規(guī)格的放大器可以抑制傳感器兩個輸出端出現(xiàn)的任何電壓,即共模電壓。

除了抑制傳感器輸出端的共模電壓,系統(tǒng)中的差模信號還有其他好處。一個好處是高共模抑制使系統(tǒng)更加穩(wěn)固,能夠抵抗電磁干擾(EMI)。外部EMI會將噪聲引入差模信號的兩個導體;差動放大器會抑制這種共模噪聲,保留并放大目標差模信號,從而獲得出色的信噪比(SNR)。差模信號的另一個好處在于,其幅度是單端信號的兩倍,這相當于SNR增加了6 dB。輸出信號幅度加倍使差分輸入放大器在低電源電壓應(yīng)用中非常有用,在此類應(yīng)用中,電壓范圍不足以允許大信號擺幅。

用于放大精密差模信號的基本拓撲是差動放大器(圖3)。差動放大器接受差分輸入信號,抑制共模電壓(VCM),放大差分輸入電壓(VDIFF),并輸出與兩個輸入電壓之差成比例的放大單端信號。其傳遞函數(shù)為VOUT = G × (VDIFF),其中VDIFF為(V2 – V1),G為放大器電路的增益,等于比率(R2/R1)。

與單端放大器不同,共模電壓是電路的兩個輸入端(V1和V2)所共有的電壓,而不是運算放大器輸入端+IN和–IN所共有的電壓。共模電壓定義為兩個輸入電壓的平均值,VCM = (V2 + V1)/2。例如,當V1為5 V且V2為3 V時,共模輸入電壓將為4 V,差模電壓將為2 V。該2 V差模信號將在輸出端放大。

如前所述,帶有差分輸入的放大器的共模抑制比表示為CMRR = 20 × log10 (ADIFF/ACM)。請注意,由于差分增益(ADIFF)增加且共模增益(ACM)降低,共模抑制會隨著差分增益成比例改進。這是一項重大優(yōu)勢,使我們能夠同時實現(xiàn)更高的增益和更高的CMRR。另外需要注意的是,CMRR會隨著頻率的增加而降低,因此務(wù)必選擇在目標信號頻率下具有所需抑制能力的差動放大器。

圖3.差動放大器電路。

電阻容差和放大器精度

差動放大器電路的CMRR在很大程度上取決于R2/R1之比和R2’/R1’之比的匹配程度。當放大器電路由分立元件組成時(如圖3所示),可能很難實現(xiàn)良好匹配。例如,精密運算放大器的CMRR規(guī)格可達到140 dB或更高。但即便是理想的運算放大器,假設(shè)有一個4電阻差動放大器電路使用容差為0.1%的電阻且增益為1,如果在該電路中使用理想運算放大器,該電路只能實現(xiàn)54 dB的最小CMRR。1 54 dB的CMRR大約相當于僅9位ADC的精度。這對于一些應(yīng)用來說可能已經(jīng)足夠,但高精度應(yīng)用需要更好的CMRR,因此需要更好的電阻匹配。放大器電路的另一個重要規(guī)格是增益精度。若要放大信號以獲得特定增益,需要為R2、R1、R1'和R2'選擇特定的電阻值。任何偏離標稱電阻值的容差都會導致比率不匹配,從而造成增益誤差。由于所有電阻的阻值都隨著溫度而變化,因此增益溫漂會產(chǎn)生相應(yīng)的誤差。分立放大器電路的這些問題可通過良好匹配的電阻網(wǎng)絡(luò)來緩解,例如電阻比匹配率為0.01%的ADI LT5400系列,或匹配率為0.003%的LT5401系列。

為了達到最高精度,所有這些挑戰(zhàn)(CMRR降低、增益誤差增加和增益溫漂增加)以及印刷電路板上的溫度梯度、寄生電容等其他問題,都可以通過使用集成差動放大器得到大幅緩解,其中放大器和電阻都置于單芯片集成電路(IC)上。由于每個IC上的電阻值在生產(chǎn)過程中都精確匹配,因此集成差動放大器的CMRR規(guī)格非常高,且增益誤差非常低。此外,由于它們位于同一裸片上,并由相同的材料制成,每個電阻往往接近相同的溫度并具有相同的溫度系數(shù),因此它們的阻值將在溫度范圍內(nèi)表現(xiàn)出類似的變化,使得電阻比的變化非常小,因此增益溫漂也極低。許多集成差動放大器的CMRR規(guī)格高達80 dB至90 dB,甚至更高,增益誤差為0.005%至0.02%,增益溫漂低至1 ppm/°C。

下面看看ADI的集成式LT1997-1差動放大器,如圖4所示。該放大器的額定最小CMRR超過100 dB,十分出色,相當于大約17位的精度。其典型增益誤差為±0.01%,典型增益溫漂超低,為±0.2 ppm/°C。一個額外的好處是,通過集成多個具有不同值的集成電阻,系統(tǒng)設(shè)計人員可選擇針對不同增益進行配置。對于LT1997-1,多個集成電阻允許針對從0.141 V/V到80 V/V的24個獨特放大(和衰減)增益進行配置,且不使用外部元件。

圖4.LT1997-1集成差動放大器(針對10 V/V的增益配置)。

通過差動放大器實現(xiàn)電流檢測

精密電流檢測是差動放大器的一個熱門應(yīng)用,相關(guān)示例如圖5所示。流向負載的電流會流經(jīng)一個超低阻值的分流(檢測)電阻。分流電阻上的電壓與負載電流成正比。被檢測的電流會在分流電阻上產(chǎn)生成比例的小差模電壓。為了利用模數(shù)轉(zhuǎn)換器的整個輸入電壓范圍,該小電壓會被放大。

圖5中的電路被稱為高邊電流檢測,因為分流電阻放置(正在測量電流)在電源和負載之間;這不是低邊檢測,在低邊檢測中,分流電阻位于負載和地之間。高邊電流檢測有諸多優(yōu)勢,其中一個優(yōu)勢是可以在負載處檢測到對地短路。

對于高邊差模電流檢測,必須考慮兩個電壓:差模電壓(VDIFF),即輸入V2和輸入V1之間的信號電壓(分流電阻上的電壓);還有共模電壓(VCM),存在于V2和V1上。在此示例中,運算放大器的+IN輸入為電壓VSUPPLY(或VLOAD + VDIFF),運算放大器的–IN輸入為電壓VLOAD(或VSUPPLY – VDIFF)。差動放大器將放大差模電壓并抑制共模電壓。

圖5.使用差動放大器放大精密差模信號。

在高邊電流檢測等許多應(yīng)用中,共模輸入電壓可能遠大于差模電壓的幅度。事實上,共模輸入電壓通常遠大于運算放大器的電源電壓,有時高達數(shù)百伏。由于輸出端的共模誤差與輸入端的共模電壓成正比,因此具有極高共模輸入電壓的系統(tǒng)需要相應(yīng)的高CMRR,才能獲得精確的模擬輸出信號。差動放大器的一個關(guān)鍵特性是,它能夠抑制高共模電壓,遠超出電源電壓范圍。這是可能做到的,因為每個輸入端的電阻網(wǎng)絡(luò)會衰減輸入電壓V1和V2,直至運算放大器輸入+IN和–IN在額定輸入電壓范圍內(nèi)。例如,ADI公司的AD8479接受±600 V的共模輸入電壓和±15 V的電源電壓。

電平轉(zhuǎn)換

差動放大器電路的另一個好處是,它可以非常輕松地對輸出電壓進行電平轉(zhuǎn)換。為此,許多差動放大器都包含基準輸入。當輸入端之間的差值為零時,向基準輸入引腳施加電壓可將輸出設(shè)置為該電壓。借助此功能,我們能夠?qū)⒎糯笃鬏敵雠c選定的基準電壓對齊,比如電源電壓的一半,以通過單電源進行雙向檢測(圖6);或ADC輸入電壓范圍的中點,以實現(xiàn)最佳動態(tài)范圍(圖7)。

圖6.電平轉(zhuǎn)換,使輸出電壓始終以電源電壓的一半為參考。

舉個例子,如果有一個信號在±2.5 V之間振蕩,并且目標是將該信號饋入輸入電壓范圍為0 V至5 V的ADC,那么需要將信號集中于ADC滿量程輸入電壓范圍的一半,以便利用整個輸入范圍。圖7顯示了實現(xiàn)此目標的直接方法。或者,可以向兩個REF輸入引腳施加單電壓,以直接建立輸出偏置電壓。

圖7.電平轉(zhuǎn)換,使輸出以ADC基準電壓的一半為參考。

電流檢測放大器

如前所述,單芯片差動放大器適合許多應(yīng)用,其中一個常見的應(yīng)用是使用低阻值分流電阻進行電流檢測。雖然差動放大器適用于許多電流檢測應(yīng)用,但通過對電流檢測放大器提供的某些特性和規(guī)格進行優(yōu)化,其他應(yīng)用也可從中受益。這些專用放大器的架構(gòu)通常與差動放大器不同。CSA往往使用高電壓輸入晶體管,以直接接受快速變化的大共模電壓,同時精確放大小的差模分流電壓(圖8),而不是使用輸入電阻網(wǎng)絡(luò)來衰減輸入電壓。

圖8.電流檢測放大器的示例。

在差動放大器中,輸入差模信號在內(nèi)部由電阻網(wǎng)絡(luò)衰減,然后放大到其原始輸入電平,再加上更多增益,從而在輸出端實現(xiàn)最終信號放大。將衰減的輸入恢復到原始信號幅度會消耗內(nèi)部放大器的部分增益帶寬積,為了獲得額外的增益而放棄一些帶寬。由于大多數(shù)CSA的高壓輸入晶體管不衰減信號,因此不需要增益來恢復信號幅度,并且內(nèi)部運算放大器提供更多可用帶寬來放大信號。例如,AD8206差動放大器的小信號-3 dB帶寬為100 kHz,而AD8210電流檢測放大器的帶寬為450 kHz。CSA的帶寬增加使其非常適合高頻應(yīng)用,或者適合在檢測快速電流瞬變時使用。

此外,與CMRR為80 dB至100 dB的大多數(shù)差動放大器相比,CSA往往具有更高的共模抑制比,范圍在100 dB至120 dB,甚至更高。請注意,CSA的大帶寬有一個缺點,那就是它不具備內(nèi)部衰減網(wǎng)絡(luò),因此無法像差動放大器一樣接受非常高的共模輸入電壓電平,但CSA共模電壓限值仍然非常高,介于80 V到100 V之間。

CSA通常用于測量大開關(guān)電流。在負載的高邊測量開關(guān)電流(即分流電阻上的差模電壓)時,分流電阻的共模電壓通常可以在接地和電源電壓之間快速變化。共模電壓的快速變化會在放大器輸入端引起大瞬變。這些共模電壓瞬變經(jīng)常會超過信號幅度。理想情況下,放大器產(chǎn)生的輸出僅反映放大的差模檢測電壓。實際上,共模階躍響應(yīng)可能出現(xiàn)在輸出端。CSA專門用于抑制此類快速變化的共模電壓階躍產(chǎn)生的共模瞬態(tài)尖峰,因此非常適合對幅度快速變化的信號進行電流檢測。

圖9顯示了ADI公司的AD8418 CSA所實現(xiàn)的階躍響應(yīng)和瞬態(tài)抑制。共模輸入電壓為15 V,放大器的輸入瞬變過沖共模電壓超出50%。產(chǎn)生的共模階躍響應(yīng)表現(xiàn)為僅36 mV的短暫輸出擾動。

圖9.AD8418共模瞬態(tài)電壓響應(yīng)(VSUPPLY = 5 V)。

舉個例子,在典型的三相電機控制系統(tǒng)中測量相位電流時,會發(fā)生共模電壓快速切換,在該場景中,控制器將脈寬調(diào)制(PWM)信號驅(qū)動到逆變器級,然后逆變器級驅(qū)動電機的每一側(cè)(圖10)。分流電阻與電機并排放置。利用分流電阻上瞬時電流測量的差模電壓反饋,控制器能夠確定每個信號的相位。通過每個PWM脈沖,分流電阻上的共模電壓在V–和V+之間的整個電源電壓范圍內(nèi)快速步進。這些快速PWM步進要求放大器具有高帶寬,且能夠在上升沿和下降沿抑制高瞬態(tài)過沖。ADI公司的AD8411A在輸入端集成了共模電壓范圍高達70 V的精密內(nèi)部電阻分壓器網(wǎng)絡(luò),采用2.7 MHz高帶寬,并包含去毛刺電路,以通過降低快速開關(guān)輸入信號的影響來實現(xiàn)輸出精度,因此非常適合這類應(yīng)用。

圖10.三相電機控制電流測量。

儀表放大器

到目前為止討論的差分輸入放大器拓撲(差動放大器和電流檢測放大器)非常適合用于在廣泛應(yīng)用中放大差模信號,特別是在存在極高共模電壓的情況下。對于需要在高共模電壓中(包括噪聲)以高精度放大極小信號的應(yīng)用,使用具有更高精度的放大器必不可少。儀表放大器(in-amps)專為這些嚴苛的應(yīng)用而設(shè)計。

與儀表放大器相比,差動放大器的一個潛在局限是輸入阻抗相對較低。另一個局限是每個放大器輸入的阻抗不相等。要了解這些局限的影響,可參考惠斯通電橋(圖11)中的差模信號(V2 – V1)放大,這種配置廣泛用于各種傳感器。首先要考慮的是,許多電橋的輸出阻抗較高,卻要驅(qū)動相對較低的放大器輸入阻抗,這可能是個問題。例如,當電橋輸出阻抗為4 k?,差動放大器輸入阻抗為200 k?時,其輸出阻抗上將損失2%的傳感器信號,這將導致測量精度降低。第二個要考慮的是,差動放大器的輸入阻抗不相等,這將導致電橋電路兩側(cè)的壓降不同,從而產(chǎn)生差模電壓誤差。為了解決這些問題,所使用的放大器需要具有更高的輸入阻抗,在電橋輸出上呈現(xiàn)平衡負載,并具有出色的CMRR。這些都是儀表放大器的主要特性和優(yōu)點。

圖11.惠斯通電橋

觀察經(jīng)典的3運算放大器儀表放大器(圖12a),兩個運算放大器A1和A2組成第一級(稱為前置放大器級),第三個運算放大器A3用于第二級(稱為減法器)。減法器級可識別為熟悉的差動放大器拓撲。放大器A1和A2提供平衡且極高的輸入阻抗。此外,它們會放大差模輸入電壓,而將共模電壓直接傳遞而不進行放大。A3處的減法器級會抑制共模電壓,并將放大的差模電壓傳遞至輸出端。這種拓撲的另一個特性是,系統(tǒng)設(shè)計人員可以通過單個外部電阻(RG)設(shè)置增益,因而無需匹配分立電阻比。這種拓撲非常適合用于放大非常小的信號并抑制高共模電壓。該儀表放大器的傳遞函數(shù)為VOUT = G × (VDIFF) + VREF,其中VDIFF為(V+IN – V+IN),G是儀表放大器的增益,VREF是施加到REF輸入端的電壓,用于對輸出電壓進行電平搬移。

與差動放大器一樣,集成儀表放大器(圖12b)也受益于單芯片裸片上精確匹配的電阻。雖然集成差動放大器的共模抑制范圍可能介于90 dB至100 dB之間,但許多儀表放大器的CMRR規(guī)格可達130 dB至140 dB,甚至更高。這得益于儀表放大器的大差模增益。在前面的電橋示例中,假設(shè)電橋源電阻為4 kΩ,而ADI AD8422儀表放大器的輸入電阻為200 GΩ,源信號損耗非常小,為0.000002% (0.02 ppm)。此外,儀表放大器的輸入偏置電流往往遠低于差動放大器。因此,當輸入偏置電流流過任何源電阻時,產(chǎn)生的電壓誤差將較小。

圖12.(a) 3運算放大器儀表放大器拓撲和(b)單芯片儀表放大器集成電路。

全差分放大器

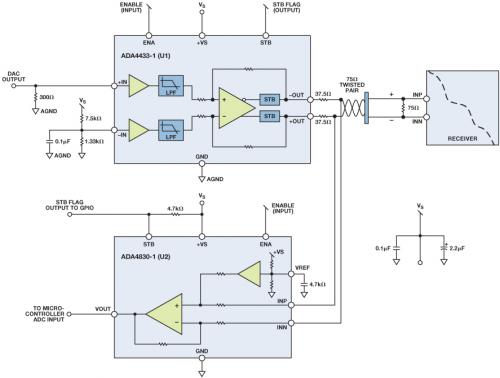

前文探索了具有單輸入和差分輸入的放大器拓撲,這些拓撲均具有單端輸出。在精密信號放大器電路設(shè)計中,可能需要生成差分輸出信號。具有差分輸入和差分輸出的放大器被稱為全差分放大器(有時縮寫為FDA或diff-amp)。集成FDA用途廣泛,能夠放大單端或差分輸入信號。在抑制輸入共模電壓、放大差分輸入電壓和提供差分輸出信號方面,F(xiàn)DA均表現(xiàn)出色。通過為基準輸入引腳施加所需的電壓電平,可確定輸出共模電壓(VOCM)。

圖13.全差分放大器驅(qū)動高精度ADC(參考電路筆記CN-0310)。

FDA的一個常見應(yīng)用是驅(qū)動高性能ADC的差分輸入。在這種情況下,F(xiàn)DA可用于將小輸入信號放大到ADC的輸入電壓范圍內(nèi),或?qū)⒋筝斎胄盘査p到ADC的輸入電壓范圍內(nèi)。圖13顯示了ADI公司的AD8475FDA接收來自傳感器的差分輸入信號,然后驅(qū)動24位、250 kSPS Σ-Δ ADC(AD7176-2)的差分輸入。在該應(yīng)用中,放大器的VOCM輸入由ADC的基準輸出驅(qū)動,以將共模電壓設(shè)置為適合ADC輸入動態(tài)范圍的電平。

FDA的另一個普遍應(yīng)用是將單端輸入信號轉(zhuǎn)換為差分輸出信號。許多傳感器會輸出高精度單端信號。在放大或衰減信號并隨后驅(qū)動差分ADC輸入時,需要將單端信號轉(zhuǎn)換為差分信號。FDA非常適合執(zhí)行此類任務(wù)。圖14顯示了這種配置,將一個放大器輸入接地,并使用單端信號驅(qū)動另一個輸入。除了調(diào)理ADC差分輸入的信號,轉(zhuǎn)換為差分輸出還能夠使信號幅度加倍(6 dB),從而提高SNR并優(yōu)化數(shù)字化信號的有效分辨率。

圖14.單端至差分信號轉(zhuǎn)換。

結(jié)論

對于精密信號調(diào)理電路,放大器拓撲的選擇取決于多個考慮因素。一些優(yōu)先考慮因素包括信號類型(單端或差分)、信號源阻抗(例如,傳感器)、所需的共模抑制和增益精度。通過利用本文中介紹的各種放大器拓撲,外加ADI公司提供的采用所有這些拓撲的放大器,系統(tǒng)設(shè)計人員能夠?qū)⒑线m的放大器與自身的應(yīng)用相匹配,從而實現(xiàn)理想的系統(tǒng)性能。

參考文獻

1 Ramón Pallás-Areny和John G. Webster,“Common Mode Rejection Ratio in Differential Amplifiers”,IEEE儀器儀表與測量匯刊,第40卷,第4期,1991年8月。

Paul Blanchard和Anna Fe Briones,“AN-1308:電流檢測放大器共模階躍響應(yīng)”,ADI公司,2015年10月。

Kristina Fortunado,“AN-1321:電流檢測應(yīng)用中的共模瞬變”。ADI公司,2014年10月。

Harry Holt,“深入考察差動放大器”,《模擬對話》,第48卷第1期,2014年2月。

Walt Jung,《運算放大器應(yīng)用手冊》,ADI公司,2005年。

Kester Walt,“MT-068:差動和電流檢測放大器”,ADI公司,2008年10月。

Kester Walt,“MT-074:精密ADC用差分驅(qū)動器”,ADI公司,2008年10月。

Charles Kitchin和Lew Counts,《儀表放大器應(yīng)用工程師指南》第3版,ADI公司,2006年。

Henri Sino,“高側(cè)電流檢測:差動放大器與電流檢測放大器”,模擬對話,第42卷第1期,2008年1月。

評論