dsp+fpga 文章 最新資訊

AC-Link數(shù)字音頻VHDL編/解碼的FPGA設計

- ?????? 提出一種利用FPGA實現(xiàn)AC-Link數(shù)字音頻處理的設計方案.AC-Link音頻編解碼系統(tǒng)以VHDL模塊進行設計,經(jīng)過波形仿真和結果驗證后,將程序下載到FPGA中實現(xiàn)1這種設計方法可以縮短設計周期,提高設計的可靠性和效率。 ??????? 引言 ??????? 數(shù)字音頻處理是指為真

- 關鍵字: AC-Link VHDL FPGA

FPGA在語音存儲與回放系統(tǒng)中的應用

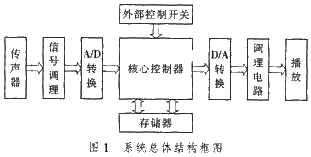

- 1 引言 隨著數(shù)字信號處理器、超大規(guī)模集成電路的高速發(fā)展,語音記錄技術已從模擬錄音階段過渡到數(shù)字錄音階段。在數(shù)字化錄音技術中,壓縮后的語音數(shù)據(jù)有些存儲在硬盤中,有些存儲在帶有掉電保護功能的RAM或FLASH存儲器中。筆者介紹的語音存儲與回放系統(tǒng),未使用專用的語音處理芯片,不需要擴展接口電路,只利用FPGA作為核心控制器,就能完成語音信號的數(shù)字化處理,即實現(xiàn)語音的存儲與回放。 2 系統(tǒng)總體結構 數(shù)字化語音存儲與回放系統(tǒng)的基本工作原理是將模擬語音信號通過模數(shù)轉換器(A/D)轉換成數(shù)字信號

- 關鍵字: FPGA

基于DVD-ROM應用的內容加擾系統(tǒng)的VLSI設計

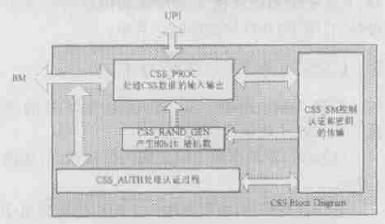

- 摘 要:本文介紹了一種基于DVD-ROM應用的內容干擾系統(tǒng)(CSS)的設計和實現(xiàn)。該系統(tǒng)可有效防止對DVD盤片的非法拷貝。文中通過對其工作原理和實際應用的分析,給出其最終實現(xiàn)方案,并用Verilog HDL完整整個系統(tǒng)的設計。功能仿真和FPGA驗證表明,設計成功。 關鍵詞:內容加擾系統(tǒng);DVD;Verilog HDL;FPGA驗證 引 言 DVD-ROM的視頻和音頻數(shù)據(jù)是經(jīng)過加密編碼的,加擾的源是標題密鑰(Tittle Key),同時標題密鑰被光盤密鑰(光盤密鑰)加密,主機在播放影碟

- 關鍵字: FPGA DVD CSS VLSI

定點DSP C55X實現(xiàn)浮點相關運算

- 引 言 DSP結構可以分為定點和浮點型兩種。其中,定點型DSP可以實現(xiàn)整數(shù)、小數(shù)和特定的指數(shù)運算,它具有運算速度快、占用資源少、成本低等特點;靈活地使用定點型DSP進行浮點運算能夠提高運算的效率。目前對定點DSP結構支持下的浮點需求也在不斷增長,主要原因是:實現(xiàn)算法的代碼往往是采用C/C++編寫,如果其中有標準型的浮點數(shù)據(jù)處理,又必須采用定點DSP器件,那么就需要將浮點算法轉換成定點格式進行運算。同時,定點DSP結構下的浮點運算有很強的可行性,因為C語言和匯編語言分別具有可移植性強和運算效率高的

- 關鍵字: DSP

使用FPGA測試的一些有效方法

- 引言 隨著芯片設計技術越來越成熟,越來越多的產(chǎn)品選擇使用SoC(System on Chip)的技術實現(xiàn)。然而,每一次流片不一定都能達到預期的效果。根據(jù)Synopsys公司統(tǒng)計,有超過60%的公司需要重新流片(respin)。在這個過程中浪費了大量的金錢,一次修正平均的花費就超過100萬美元。如果一旦錯過了商品推出的最佳時機,那么錯過市場機會的代價則以數(shù)千萬美元計,甚至更高。據(jù)統(tǒng)計,在需要respin的芯片中有43%是在前端的設計和實現(xiàn)的時候產(chǎn)生的邏輯功能錯誤。如何避免或減小如此高的風險是每一

- 關鍵字: FPGA

基于FPGA系統(tǒng)易測試性的研究

- 引 言 現(xiàn)代科技對系統(tǒng)的可靠性提出了更高的要求,而FPGA技術在電子系統(tǒng)中應用已經(jīng)非常廣泛,因此FPGA易測試性就變得很重要。要獲得的FPGA內部信號十分有限、FPGA封裝和印刷電路板(PCB)電氣噪聲,這一切使得設計調試和檢驗變成設計中最困難的一個流程。另一方面,當前幾乎所有的像CPU、DSP、ASIC等高速芯片的總線,除了提供高速并行總線接口外,正迅速向高速串行接口的方向發(fā)展,F(xiàn)PGA也不例外。每一條物理鏈路的速度從600 Mbps到10 Gbps,高速I/O的測試和驗證更成為傳統(tǒng)專注于FPG

- 關鍵字: FPGA

基于FPGA的USB2.0虛擬邏輯分析儀的設計與實現(xiàn)

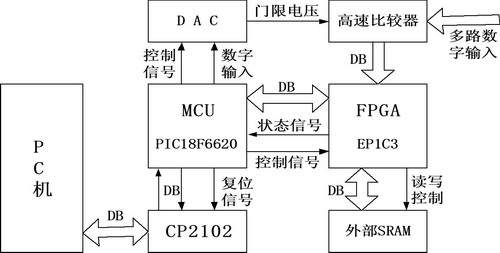

- 引言 傳統(tǒng)的邏輯分析儀體積龐大、價格昂貴、通道數(shù)目有限,并且在數(shù)據(jù)采集、傳輸、存儲、顯示等方面存在諸多限制,在很大程度上影響了其在實際中的應用。選用高性能的FPGA芯片進行數(shù)據(jù)處理,充分利用PC的強大處理功能,配合LabView圖形化語言開發(fā)的虛擬邏輯分析儀,其數(shù)據(jù)處理和傳輸速率大大提高,適用性極大增強,其顯示、操作界面和低廉的成本較之傳統(tǒng)的邏輯分析儀具有極大的優(yōu)勢和發(fā)展前景。 工作原理 本設計選用Altera公司的Cyclone系列FPGA器件EP1C3進行數(shù)據(jù)采集和處理,外接SRAM

- 關鍵字: FPGA

TMS320C6000系列DSP的軟件優(yōu)化技術

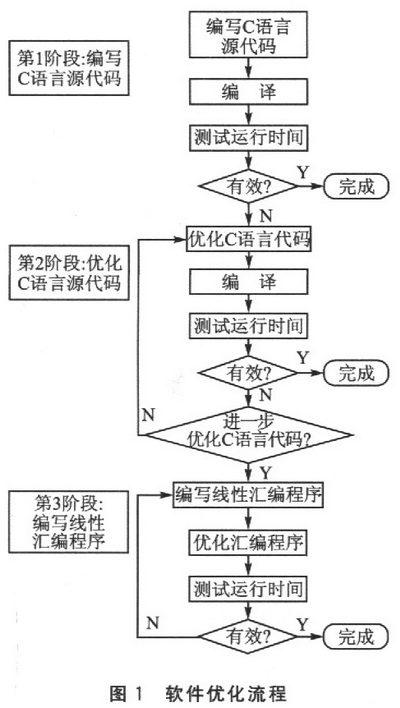

- 1 DSP系統(tǒng)的軟件優(yōu)化流程 DSP系統(tǒng)的軟件優(yōu)化流程如圖l所示。整個工作流程分為3個階段: 第l階段,直接根據(jù)需要用高級C語言實現(xiàn)DSP功能,測試代碼的正確性。然后,移植到C6X平臺,利用C6X開發(fā)環(huán)境Profile測試程序的運行時間。若不滿足要求,則進入下一階段。 第2階段,利用C6X提供的優(yōu)化方式和其他各種優(yōu)化技巧,如使用不同的編譯器選項使能軟件流水,循環(huán)展開,字存取代替半字存取等,優(yōu)化C語言代碼。如果還不能滿足要求,則進入第3階段。 第3階段,將C語言代碼中耗時最長的部

- 關鍵字: DSP

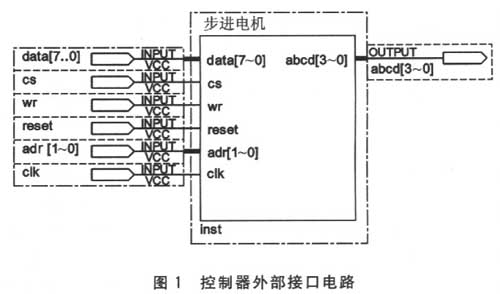

基于FPGA的步進電機控制器設計

- 步進電機是一種將電脈沖信號轉換成相應的角位移的特殊電機,每改變一次通電狀態(tài),步進電機的轉子就轉動一步。目前大多數(shù)步進電機控制器需要主控制器發(fā)送時鐘信號,并且要至少一個I/O口來輔助控制和監(jiān)控步進電機的運行情況。在單片機或DSP的應用系統(tǒng)中,經(jīng)常配合CPLD或者FPGA來實現(xiàn)特定的功能。本文介紹通過FPGA實現(xiàn)的步進電機控制器。該控制器可以作為單片機或DSP的一個直接數(shù)字控制的外設,只需向控制器的控制寄存器和分頻寄存器寫入數(shù)據(jù),即町實現(xiàn)對步進電機的控制。 1 步進電機的控制原理 步進電機是數(shù)

- 關鍵字: FPGA

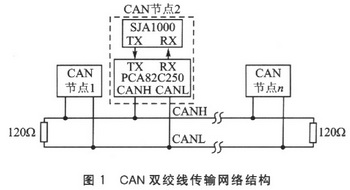

一種CAN息線光纖傳輸接口設計

- 摘要 在分析CAN總線雙絞線和光纖傳輸特點的基礎上,提出一種基于光纖收發(fā)一體模塊及CAN總線控制器SJAl000的光纖傳輸接口設計方案;詳細介紹光纖收發(fā)器的選取及傳輸接口的實現(xiàn);根據(jù)光纖收發(fā)一體模塊對信號源時鐘提取的要求以及CAN總線的非破壞性總線仲裁的特點,設計了一種CAN總線信號編解碼方法,井用FPGA加以實現(xiàn);通過實際的通信實驗驗證了設計方案的正確性,并根據(jù)實驗數(shù)據(jù)對CAN總線在兩種介質下的傳輸性能作了比較。 關鍵詞 CAN總線 光纖 傳輸接口 FPGA 引 言 作為一種成熟的

- 關鍵字: CAN總線 光纖 傳輸接口 FPGA

FPGA如何同DDR3存儲器進行接口?

- 大家好,我叫Paul Evans,是Stratix III產(chǎn)品營銷經(jīng)理。到目前為止,我已經(jīng)從事了6年的雙倍數(shù)據(jù)速率存儲器工作,今天和大家一起討論一下DDR3。DDR3的主要難題之一是它引入了數(shù)據(jù)交錯,如屏幕上所示。 為了更好地進行演示,我們將使用這里所示的Stratix III DDR3存儲器電路板。它上面有幾個高速雙倍數(shù)據(jù)速率存儲器,例如DDR2 UDIMM插槽、RLD RAM、QDR,當然,還有DDR3 UDIMM插槽。因此,我們所要做的就是通過Quartus軟件來下載一個簡單設計,F(xiàn)PGA

- 關鍵字: FPGA DDR3 存儲器

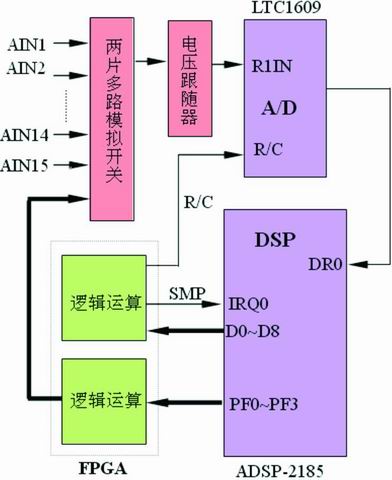

多路交流異步采樣及DSP軟件校準技術

- 摘要: 本文介紹了一種在DSP平臺下對多路交流信號采樣時采用的一種異步采樣方法。 關鍵詞: 交流采樣;校準;DSP 引言 在對電力線路的電壓和電流進行測量時,為使測量值具有較高的精度,一般都采用交流采樣技術。目前,比較常用的交流采樣方法是:在交流信號的一個周期內,等間隔采樣N點數(shù)據(jù),然后利用傅立葉變換,計算出基波及一些諧波的有效值,為衡量供電質量通常還要求計算出各信號的相位。但由于同一測量裝置要同時對很多路電壓和電流量進行采樣,而采樣所用的A/D的輸入又有限,不可能對電壓和電流量同時

- 關鍵字: 交流采樣 校準 DSP 200803

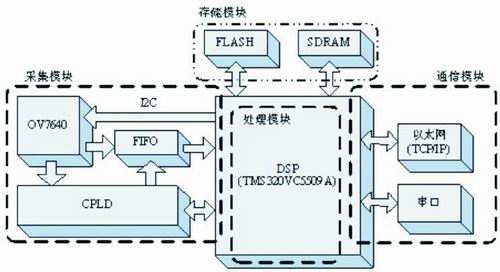

基于以太網(wǎng)的嵌入式視覺傳感器*

- 隨著計算機科學和自動控制技術的發(fā)展,視覺系統(tǒng)被廣泛用于工業(yè)檢測、生物醫(yī)學、軍事偵察等領域。嵌入式視覺系統(tǒng),是將圖像的采集、處理與通信功能集成于單一相機內,從而提供了具有多功能、模塊化、高可靠性、易于實現(xiàn)的機器視覺解決方案。同時,視覺傳感器需要通過網(wǎng)絡化設計完成控制信息、圖

- 關鍵字: CMOS圖像傳感器 DSP 以太網(wǎng) 圖像采集 200803

dsp+fpga介紹

您好,目前還沒有人創(chuàng)建詞條dsp+fpga!

歡迎您創(chuàng)建該詞條,闡述對dsp+fpga的理解,并與今后在此搜索dsp+fpga的朋友們分享。 創(chuàng)建詞條

歡迎您創(chuàng)建該詞條,闡述對dsp+fpga的理解,并與今后在此搜索dsp+fpga的朋友們分享。 創(chuàng)建詞條

關于我們 -

廣告服務 -

企業(yè)會員服務 -

網(wǎng)站地圖 -

聯(lián)系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司