沙子里長出的奇跡:一文讀懂芯片

你手中的手機、每天辦公的電腦,甚至是家里的智能家電,它們的核心大腦都是芯片。但很少有人知道,這個撐起了數字時代的精密產物,最初居然只是毫不起眼的沙子。今天我們就一起走進芯片的世界,從砂石到方寸算力之巔,看看芯片是如何誕生,又有著怎樣精妙的內在構造。

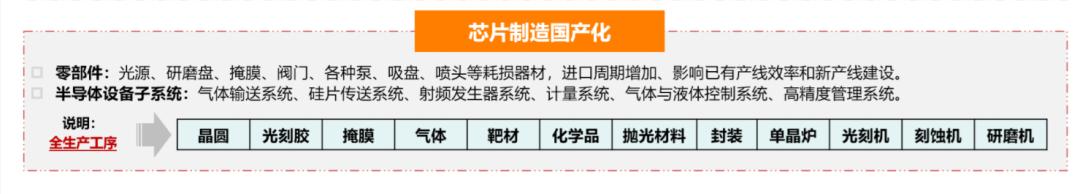

一、從沙子到芯片 —— 理解芯片的生產

點石成金的第一步:提純硅

從沙子到芯片的第一步,就是從石英砂中提取高純度硅,這一步就像給沙子“脫胎換骨”,去除雜質、保留純凈的硅元素,為后續芯片制造打下基礎。

石英砂并不能直接變成芯片,第一步要做的就是“提純”。工廠會將石英砂放入溫度超過1800℃的高溫電弧爐中,加入碳元素進行還原反應,去除石英砂中的氧元素,提煉出純度約98%的工業硅。不過,此時的工業硅還像一塊“粗坯”,含有大量鐵、鋁、硼等雜質,無法用于精密的芯片制造。

接下來要進行更精細的提純——西門子法。簡單來說,就是先將工業硅轉化為三氯氫硅氣體,再通過多次精餾(類似“蒸餾提純”的原理),將三氯氫硅還原為高純度的電子級多晶硅。這種多晶硅的純度高達99.999999999%(11個9),意味著100億個原子中,最多只能有1個雜質原子,其純度遠超我們日常接觸的任何物質,哪怕是醫用級別的高純度材料,也無法與之相比。這一步,就是把普通沙子“點石成金”的關鍵。

晶圓

高純度的多晶硅,還需要進一步加工成“晶圓”——芯片的“載體”。工人會將多晶硅融化成熔融狀態的硅液,放入單晶爐中,再將一顆提前準備好的“籽晶”(可以理解為“種子”)放入硅液中。通過“旋轉提拉法”,籽晶會以每分鐘幾毫米的緩慢速度向上提拉,硅原子會順著籽晶的晶格結構,一層一層整齊排列,最終形成一根完整的單晶硅棒。

單晶硅棒的直徑,決定了后續晶圓的尺寸。目前主流的晶圓尺寸是12英寸(約30厘米),一根12英寸的單晶硅棒,長度可以達到2米以上,堪比一個成年人的身高。隨后,單晶硅棒會被金剛石鋸片切割成厚度僅0.75毫米左右的薄片——這就是硅片。

切割后的硅片表面會有劃痕和凹凸不平,需要經過打磨和化學機械拋光,去除表面損傷,最終得到表面如鏡面般光滑的晶圓。它的表面平整度誤差不超過0.1納米,相當于人類頭發絲直徑的百萬分之一——如果把晶圓放大到足球場那么大,它的表面最高處和最低處的差距,也不會超過一根頭發絲的粗細。

光刻與蝕刻:在晶圓上繪制電路

如果說晶圓是芯片的“畫布”,那么光刻和蝕刻,就是在這張“畫布”上繪制精密電路的核心步驟——這也是芯片制造中最關鍵、最難的一步,被稱為半導體產業的“皇冠上的明珠”,直接決定了芯片的精度和性能。

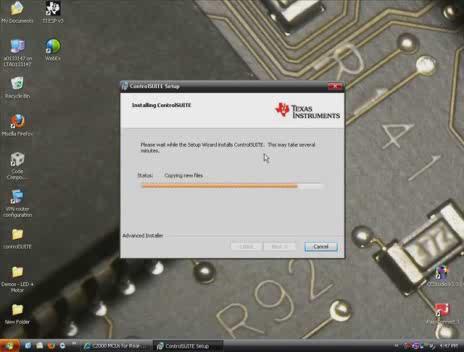

首先,工程師會在晶圓表面涂上一層“光刻膠”,這種材料遇到特定光線會發生化學性質變化。隨后,使用光刻機(目前最先進的是極紫外光刻機EUV),將設計好的芯片電路圖,通過極紫外光投射到光刻膠上。曝光后的光刻膠會變硬,形成一層可以抵抗蝕刻的“保護層”,而未曝光的部分則會保留柔軟的狀態。

目前最先進的極紫外光刻機,其光源能量是太陽光的100萬倍,能夠實現0.5納米的制程精度——這個精度有多高?相當于把一根頭發絲分成100萬份,每一份的寬度,就是它的精度。這種超高精度,才能讓芯片上集成更多的晶體管,實現更強的算力。

光刻完成后,晶圓會被放入蝕刻機中。蝕刻機通過等離子體(一種高溫帶電氣體),將沒有被光刻膠保護的硅材料“腐蝕”掉,只留下被光刻膠覆蓋的部分,這樣一來,晶圓表面就會出現精細的電路圖案。這個過程并不是一次就能完成的,需要重復幾十次甚至上百次,每一次的對準精度都要控制在納米級別,稍有失誤,整片晶圓就會報廢,損失巨大。

摻雜與封裝:賦予芯片功能與保護

有了電路圖案的晶圓,還只是“半成品”,需要通過“摻雜”工藝,賦予它計算能力。摻雜的原理很簡單:通過離子注入工藝,將磷、硼等雜質離子加速到接近光速,精準注入到晶圓的特定區域,改變半導體的導電性能,從而形成晶體管的源極、漏極和柵極——這三個部分,就是晶體管的“核心部件”,相當于芯片的“最小計算單元”。

離子注入的精度要求極高,深度和濃度的誤差不能超過一個原子層,稍有偏差,晶體管就無法正常工作。完成摻雜后,晶圓會被送到測試機上,通過細小的探針,測試每一顆芯片的電氣性能,篩選出合格的芯片裸片(相當于芯片的“核心裸板”),不合格的會被直接淘汰。

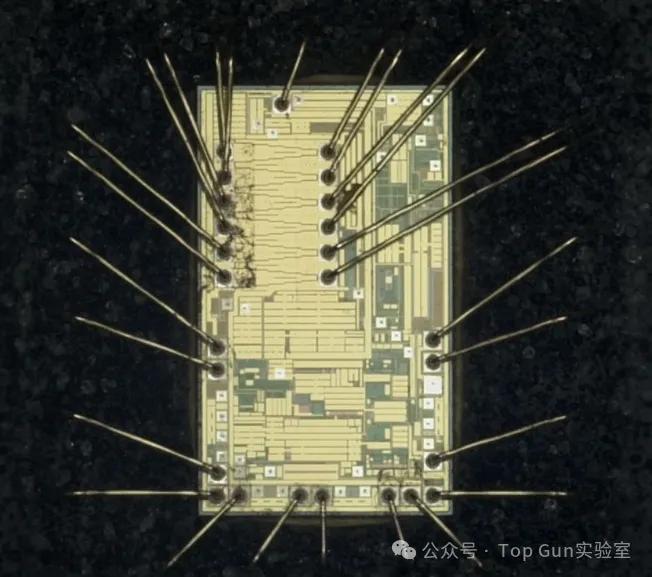

最后一步是封裝。封裝就像是給芯片“穿上一層堅固的鎧甲”:首先通過金絲球焊工藝,將直徑僅20微米(比頭發絲還細)的金線,精準焊接在芯片裸片的焊盤和封裝引腳之間;隨后,用環氧樹脂等耐高溫、防腐蝕的材料,將芯片裸片包裹起來,形成我們日常見到的芯片成品。

封裝不僅僅是保護作用,還承擔著散熱和電氣連接的功能——芯片運行時會產生熱量,封裝材料可以幫助散熱,避免芯片因過熱損壞;而引腳則是芯片與外部設備(如手機、電腦主板)連接的“橋梁”,保障電信號和數據的傳輸。

二、深入了解 IC 內部結構 —— 理解芯片的設計

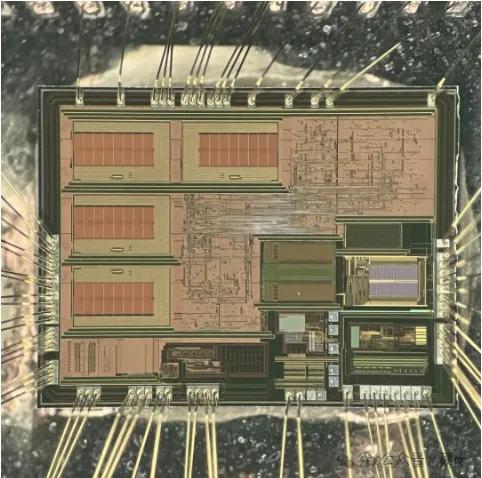

5.2.1 金線:芯片的神經脈絡

金線是芯片內部的“信號傳輸通道”,相當于芯片的“神經脈絡”,它的核心作用是連接芯片裸片和封裝引腳,快速傳輸芯片運行時的電信號。金線的優勢很明顯——導電性極佳、穩定性強,能確保電信號傳輸不延遲、不損耗,是目前芯片封裝中最常用的導線。

金線的焊接過程堪稱“微觀級別的精密操作”:通過金絲球焊工藝,首先在芯片焊盤上,用高壓電弧將金線融化成一個微小的金球(直徑僅幾微米),隨后將金球精準按壓在焊盤上,形成牢固的焊接點;接著,將金線拉到封裝引腳的位置,再次焊接固定,整個過程的精度控制在微米級別,堪比“在針尖上跳舞”。

隨著芯片集成度越來越高(芯片上的晶體管數量越來越多),金線也逐漸面臨“空間不足”的問題。因此,銅線和鋁線也開始被廣泛應用——它們的成本更低,且可以實現更高的傳輸密度,適合用于高端芯片的封裝。

5.2.2 晶圓:芯片的孕育溫床

晶圓是芯片的“孕育溫床”,所有芯片的制造,都要在晶圓上完成。一塊12英寸的晶圓,相當于一張普通唱片的大小,上面可以同時制造數千顆芯片——就像在一張紙上印上很多相同的圖案,批量生產能大幅降低成本。

每一顆芯片在晶圓上都擁有獨立的電路單元,從光刻、蝕刻到摻雜,每一道工序都需要在無塵車間中進行。無塵車間的要求極高,車間內的塵埃顆粒直徑不能超過0.1微米,空氣質量是醫院手術室的1000倍——因為哪怕是一顆微小的塵埃,落在晶圓上,都可能導致芯片電路短路,直接報廢。

當晶圓完成所有制造工序后,會通過劃片機進行切割。劃片機使用金剛石刀片,以每分鐘數萬轉的速度高速旋轉,將晶圓切割成一顆顆獨立的芯片裸片。這個過程既要保證切割精度,不能損傷芯片內部的電路,又要提高效率,確保每一顆裸片都能正常使用。

Gold Bonding Wire: 半導體鍵合金線/金絲

用于半導體封裝工藝中的芯片鍵合。

Wire Bond/金線鍵合:指在對芯片和基板間的膠粘劑處理以使其有更好的粘結性能后,用高純金線把芯片的接口和基板的接口鍵合。

成分為金(純度為99.999%),摻雜銀、鈀、鎂、鐵、銅、硅等元素。

摻雜不同的元素可以改變金線的硬度、剛性、延展度、電導率等參數。

5.2.3 封裝:芯片的堅固鎧甲

很多人以為封裝只是“給芯片套個殼”,其實不然——封裝是芯片不可或缺的一部分,承擔著機械保護、電氣連接、散熱三大核心作用,直接影響芯片的穩定性和使用壽命。

不同的應用場景,需要不同的封裝形式。比如我們常見的BGA封裝(球柵陣列封裝),擁有密集的引腳,能實現高速的數據傳輸,適合用于高性能處理器(如電腦CPU、手機SoC);而QFP封裝(四方扁平封裝),擁有扁平的引腳,更便于焊接,常用于一些通用芯片(如家電中的控制芯片)。

對于高性能芯片(如服務器芯片、顯卡芯片),封裝技術尤為重要。這類芯片運行時會產生大量熱量,普通的封裝無法滿足散熱需求,因此會采用液冷封裝技術——在封裝內部加入冷卻液,通過冷卻液的循環,快速帶走芯片產生的熱量,讓芯片可以在更高的頻率下穩定運行,發揮更強的性能。

先進封裝

先進封裝是“超越摩爾”(More than Moore)時代的一大技術亮點。當芯片在每個工藝節點上的微縮越來越困難、也越來越昂貴之際,工程師們將多個芯片放入先進的封裝中,就不必再費力縮小芯片了。本文將對先進封裝技術中最常見的10個術語進行簡單介紹。

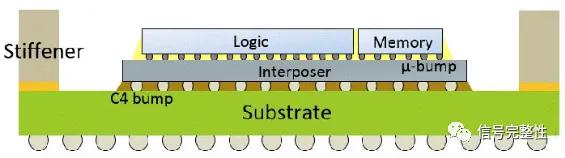

2.5D封裝

先進封裝是“超越摩爾”(More than Moore)時代的一大技術亮點。當芯片在每個工藝節點上的微縮越來越困難、也越來越昂貴之際,工程師們將多個芯片放入先進的封裝中,就不必再費力縮小芯片了。本文將對先進封裝技術中最常見的10個術語進行簡單介紹。

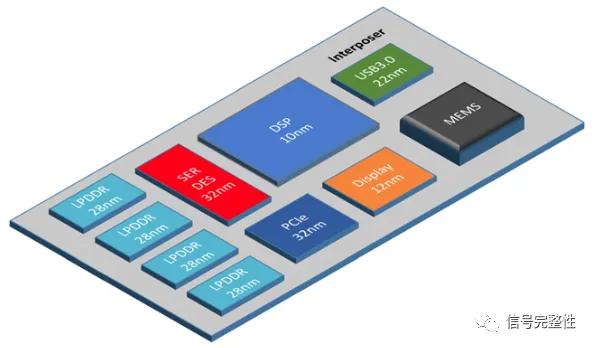

2 .5D封裝是傳統2D IC封裝技術的進展,可實現更精細的線路與空間利用。在2.5D封裝中,裸晶堆棧或并排放置在具有硅通孔(TSV)的中介層(interposer)頂部。其底座,即中介層,可提供芯片之間的連接性。

2.5D封裝通常用于高端ASIC、FPGA、GPU和內存立方體。2008年,賽靈思(Xilinx)將其大型FPGA劃分為四個良率更高的較小芯片,并將這些芯片連接到硅中介層。2.5D封裝由此誕生,并最終廣泛用于高帶寬內存(HBM)處理器整合。

2.5D封裝示意圖

3D封裝

在3D IC封裝中,邏輯裸晶堆棧在一起或與儲存裸晶堆棧在一起,無需建構大型的系統單芯片(SoC)。裸晶之間透過主動中介層連接,2.5D IC封裝是利用導電凸塊或TSV將組件堆棧在中介層上,3D IC封裝則將多層硅晶圓與采用TSV的組件連接在一起。

TSV技術是2.5D和3D IC封裝中的關鍵使能技術,半導體產業一直使用HBM技術生產3D IC封裝的DRAM芯片。

從3D封裝的截面圖可以看出,透過金屬銅TSV實現了硅芯片之間的垂直互連Chiplet

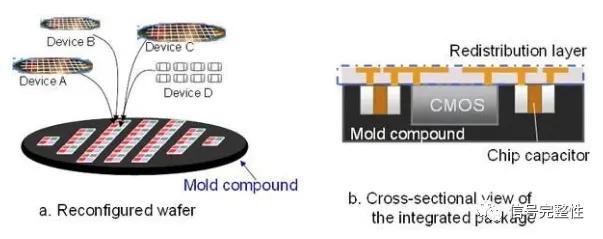

芯片庫中有一系列模塊化芯片可以采用裸晶到裸晶互連技術整合到封裝中。Chiplet是3D IC封裝的另一種形式,可以實現CMOS組件與非CMOS組件的異質整合(Heterogeneous integration)。換句話說,它們是較小型的SoC,也叫做chiplet,而不是封裝中的大型SoC。

將大型SoC分解為較小的小芯片,與單顆裸晶相比具有更高的良率和更低的成本。Chiplet使設計人員可以充分利用各種IP,而不用考慮采用何種工藝節點,以及采用何種技術制造。他們可以采用多種材料,包括硅、玻璃和層壓板來制造芯片。

基于Chiplet的系統是由中介層上的多個Chiplet組成扇出(Fan Out)封裝

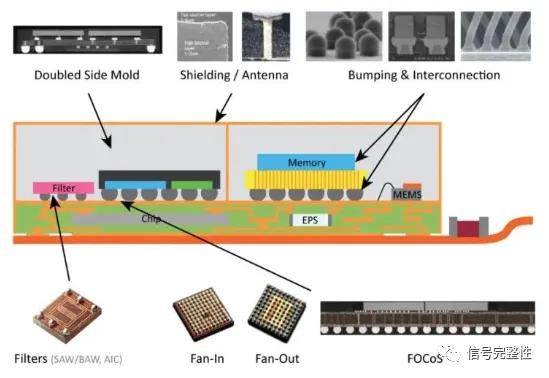

在扇出封裝中,“連結”(connection)被扇出芯片表面,從而提供更多的外部I/O。它使用環氧樹脂成型材料(EMC)完全嵌入裸晶,不需要諸如晶圓凸塊、上助焊劑、倒裝芯片、清潔、底部噴灑充膠和固化等工藝流程,因此也無需中介層,使異質整合變得更加簡單。

與其他封裝類型相比,扇出技術提供了具有更多 I/O 的小尺寸封裝。2016 年,它使 Apple 能夠使用臺積電的封裝技術將其 16 納米應用處理器與移動 DRAM 集成到 iPhone 7 的一個封裝中,從而成為技術明星。

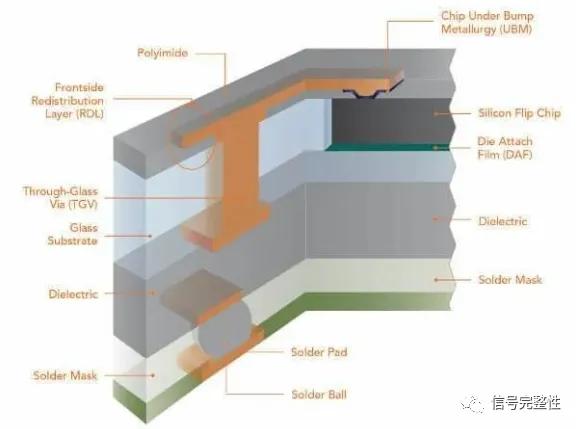

扇出封裝扇出晶圓級封裝(FOWLP)FOWLP技術是針對晶圓級封裝(WLP)的改進,可以為硅芯片提供更多外部連接。它將芯片嵌入環氧樹脂成型材料中,然后在晶圓表面建構高密度重分布層(RDL)并施加焊錫球,形成重構晶圓(reconstituted wafer)。

它通常先將經過處理的晶圓切成單顆裸晶,然后將裸晶分散放置在載體結構(carrier structure)上,并填充間隙以形成重構晶圓。FOWLP在封裝和應用電路板之間提供了大量連接,而且由于基板比裸晶要大,裸晶的間距實際上更寬松。

FOWLP封裝示例異質整合將分開制造的不同組件整合到更高級別的組件中,可以增強功能并改進工作特性,因此半導體組件制造商能夠將采用不同工藝流程的功能組件組合到一個組件中。

異質整合類似于系統級封裝(SiP),但它并不是將多顆裸晶整合在單個基板上,而是將多個IP以Chiplet的形式整合在單個基板上。異質整合的基本思想是將多個具有不同功能的組件組合在同一個封裝中。

異質整合中的一些技術建構區塊HBMHBM是一種標準化的堆棧儲存技術,可為堆棧內部,以及內存與邏輯組件之間的數據提供高帶寬信道。 HBM封裝將內存裸晶堆棧起來,并透過TSV將它們連接在一起,從而創建更多的I/O和帶寬。

HBM是一種JEDEC標準,它在封裝內垂直整合了多層DRAM組件,封裝內還有應用處理器、GPU和SoC。HBM主要以2.5D封裝的形式實現,用于高端服務器和網絡芯片。現在發布的HBM2版本解決了初始HBM版本中的容量和時鐘速率限制問題。

HBM封裝中介層

中介層是封裝中多芯片裸晶或電路板傳遞電信號的管道,是插口或接頭之間的電接口,可以將信號傳播更遠,也可以連接到板子上的其他插口。

中介層可以由硅和有機材料制成,充當多顆裸晶和電路板之間的橋梁。硅中介層是一種經過驗證的技術,具有較高的細間距I/O密度和TSV形成能力,在2.5D和3D IC芯片封裝中扮演著關鍵角色。

系統分區中介層的典型實現重分布層

重分布層包含銅連接線或走線,用于實現封裝各個部分之間的電氣連接。它是金屬或高分子介電材料層,裸晶可以堆棧在封裝中,從而縮小大芯片組的I/O間距。重分布層已成為2.5D和3D封裝解決方案中不可或缺的一部分,使其上的芯片可以利用中介層相互進行通訊。

使用重分布層的整合封裝TSV

TSV是2.5D和3D封裝解決方案的關鍵實現技術,是在晶圓中填充銅,提供貫通硅晶圓裸晶的垂直互連。它貫穿整個芯片以提供電氣連接,形成從芯片一側到另一側的最短路徑。

從晶圓的正面將通孔或孔洞蝕刻到一定深度,然后將其絕緣,并沉積導電材料(通常為銅)進行填充。芯片制造完成后,從晶圓的背面將其減薄,以暴露通孔和沉積在晶圓背面的金屬,從而完成TSV互連。

5.2.4 工藝:芯片性能的幕后推手

我們常聽到的7nm、5nm、3nm,指的就是芯片工藝(制程),它是決定芯片性能的“幕后推手”。簡單來說,制程越小,意味著晶體管的尺寸越小,在同樣大小的芯片上,就能集成更多的晶體管——晶體管數量越多,芯片的算力就越強,同時功耗也越低(更省電)。

舉個例子:從10nm工藝升級到7nm工藝,芯片的晶體管密度提升了一倍以上,功耗降低了30%左右——這就是為什么新款手機的芯片,比舊款更小、更省電,卻能實現更強的性能。先進的芯片工藝,是一個國家半導體產業實力的核心體現,它集合了材料科學、精密制造、光學、電子工程等多個領域的頂尖技術,難度極高。

目前最先進的3nm工藝,采用了全新的GAA(環繞柵極)晶體管結構——傳統的晶體管是“平面結構”,而GAA晶體管是“立體結構”,能更好地控制晶體管的電流,減少電流泄漏,進一步提升芯片的性能和能效比,為人工智能、高端計算等領域提供更強的算力支撐。

寫在最后

芯片是現代科技的集大成者,從不起眼的沙子到驅動數字世界的算力核心,每一顆芯片的誕生,都凝聚著無數工程師的智慧和心血,也承載著一個國家的科技實力。了解芯片的生產和設計,不僅能讓我們看清數字時代的底層邏輯,更能明白科技發展背后的不易——每一步突破,都需要跨越無數技術難關。

隨著半導體技術的不斷進步,未來的芯片將會擁有更加強大的算力、更低的功耗,體積也會更加小巧。它們將持續支撐人工智能、量子計算、自動駕駛等前沿科技的發展,讓數字世界變得更加智能、更加便捷,而這一切的起點,依然是那一粒平凡的沙子。

一個成功的芯片,其“突破點”往往是它在特定市場或技術領域脫穎而出的關鍵。這個突破點可以是技術上的、市場策略上的,或是商業模式上的。

評論